[반도체 소자 및 설계] Device Physics - Failure Analysis

안녕하세요!

오랜만에 "반도체 소자 및 설계" 정리로 돌아왔네요..

종강 한지가 언제고 낼모래 개강인데 말이죠..

늦었지만 이제 빨리 끝내보려 합니다 (이후로 3개정도면 끝..!)

이번 게시글은 Failurer Analysis에 대한 내용입니다.

다양한 failure에 대해 알아보고, 이를 어떻게 detection하는지에 대한 내용이겠습니다!

- Semiconductor development process

semiconductor development process는 제품, 회사, 시기에 따라 다르기 때문에 felxible한 response가 필요합니다.

처음 fab-out된 wafer의 수율, yield는 0%에서 부터 시작해, 90~100%로 올려야 합니다.

wafer 제작에서 처음으로 작동되는 chip(die)를 working die (good die)라고 하고,

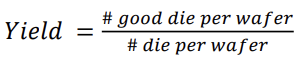

수율은 다음과 같이 나타냅니다.

wafer에 있는 총 die갯수 중 얼마나 작동이 되는지를 나타내는 것이 바로 이 yield가 되겠습니다.

margin은 구간이 변화해도 문제가 생기지 않는 범위를 말하는데,

이러한 margin을 확보하게 되면 수율이 증가하게 됩니다.

예를 들어, 10nm 박막의 margin이 [9nm-11nm]인 것이 [9.9nm-10.1nm]인 것 보다 수율이 더 높은 것이죠.

수율은 위와 같이 세가지 구간으로 나눠집니다.

prototyping은 수율이 낮은 구간,

ramp-up구간은 저수율에서 고수율으로 증가하는 구간,

manyfacturing은 고수율 구간으로 대량 생산이 가능한 구간을 말합니다.

수율 그래프는 step형태로 나타나게 됩니다.

- Yield Loss

위의 yield가 loss되는 상황은 다음 두 경우가 있습니다. 사실 크게 구분하지는 않는다고 합니다.

하나는 parametric yield loss로, 동작이 목표치를 맞추기 못한 경우입니다.

10V를 만들어야 하는 상황에서 voltage drop에 의해 5V가 만들어 진 상황이 되겠습니다.

이는 원했던 두께, 폭 사이즈, 농도, trench 구조의 폭이 달라짐 등의 다양한 이유로 발생합니다.

다른 하나는 catastrophic yield loss는 아예 동작하지 않는 경우를 말합니다.

위와 같이 10V를 만들어야 하는 상황에서 아무른 output이 없을 때가 됩니다.

이는 wafer표면에 particle이 떨어져 원치않은 open/short가 되었을 때 등에서 발생합니다.

위에서 언급했듯이, particle, 오염 잔여물, 스크래치, crystal defect, chemical impurity와 같은 defects들을 없애려면

환경 자체를 깨끗하게 하는 clean room, 몸으로 부터 보호하는 suit, HEPA filter와 같은 방법을 사용해야 합니다.

이러한 defect들은 Random 혹은 Systematic으로 유추할 수 있습니다.

위와 같은 수율 문제는 발생했을 때 유연한 대처가 필요합니다.

fab-out된 wafer에서는 open/short/leakage 또는 heat로 인한 문제가 발생합니다.

open은 연결되어야 하는 부분이 끊어진,

short는 끊어져야 하는 부분이 연결된,

leakage는 기준치 보다 많은 값이 나오는 상황을 말합니다.

heat에 의한 문제는 diffusion에 의해 발생하게 됩니다.

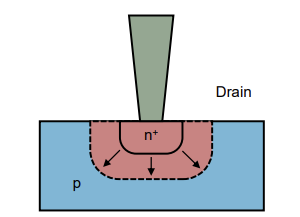

위와 같은 구조에서 만들어진 MS junction은 Na doping농도가 높아 tunneling이 일어나고, ohmic contact를 형성합니다.

이때 열로 인한 diffusion ( limited source diffusion)이 발생하면,

doping된 총 갯수는 일정하지만 면적이 넓어지기 때문에 농도가 감소, ohmic contact가 없어지면서 contact resistance가 증가하게 됩니다.

이로 인해 정확한 동작이 불가능해지고 전류 감소, 전압 증가의 결과를 초래하게 되는 것이죠.

CMP과정에서도 원하던 trench구조가 아닌 빈 공간에 가스가 차면서 void, seam과 같은 문제가 발생할 수 있습니다.

- Yield Loss Classification

위와 같은 yield loss는 EDS(Electricla Die Sorting)로 동작이 안되는 것을 분석, Bin code로 분류하게 됩니다.

위 예시에서 큰 fail값을 가진 것들, 'stand-by fail'과 'column fail'을 control하는 것이 가장 중요한 것을 알 수 있습니다.

- Failure detection

failure을 detection하는 방법은 3가②지가 있습니다. 차례대로 설명하겠습니다!

1. Electrical detection ( destructive or non-destructive) ; 전기적 측정

ET와 EDS를 이용하여 전기적으로 측정하는 방식입니다.

nanoprobing으로 예상되는 부분의 단면을 잘라 값을 측정하여 확인하고, tip으로 전압과 전류를 측정하게 됩니다.

예를 들어, DC voltage가 drop되는 상황에서를 생각해봅시다.

① leakage 가 발생했다면

junction (reverse bias)로 인한 Ioff, gate dielectric의 tunneling, metal line과 같은 이유들이 있을 수 있습니다.

② unintended resistance이 발생했다면

area, depth, concentration, chemical등에 의한 contact resistance가 발생했거나 metal line에 의해 발생합니다.

즉 다양한 상황에 대해서 발생할 수 있기 때문에 위와 같은 electrical detection을 이용합니다.

2. Phsical detection ( destructive) ; 전자 현미경

horizontally하고 vertically(cross-section)한 전자현미경으로 suspicious spot를 찾아 관찰합니다.

전자현미경은 빛과 열을 감지하는 EMMI(emission microscope)과

광학적 방법을 사용하는 광학현미경으로 나눌 수 있습니다.

광학현미경은 튀어나온 전자를 관찰하는 SEM(scanning electron microphone)과

투과한 전자를 관찰하는 TEM(transmission electorn microphone)으로 나누어 집니다.

3. Correlation analysis (unknown, non-destuctive) ; 통계적 방법

이 방법은 통계적인 방법을 말합니다.

장비, 재료, 시간, 시기, 온도와 같은 변수의 통계를 이용하여 변수의 원인을 간접적으로 알아내는 방식입니다.

위 사진의 1과 2는 늘려주는 방향, 4번은 줄여주는 방향으로 진행하면 통계적으로 좋은 결과를 내게 됩니다.

오늘의 글은 여기까지 입니다!

다양한 failure과 detection 방법을 배워보았는데요,

다음 게시글은 circuit engineering에 대한 내용인 layout에 대해 이야기 해 보겠습니다.

감사합니다!!