[반도체 공정 및 응용] Wafer&Cleaning

안녕하세요!

이번 게시글은 Wafer와 wafer를 Cleaning하는 방법들에 대해 설명해 보려 합니다.

Wafer에 사용되는 Si의 성질과 같은 간단한 설명부터 Si가 wafer로 변화는 과정, 그리고 Cleaning까지 설명하겠습니다!

< Silicon >

- Silicon의 특징

Wafer에 주로 사용하는 물질은 실리콘(Si)입니다. 이러한 Silicon의 특징은 다음과 같습니다.

- SiO2의 형태로 많이 존재 → 비용이 낮음.

- SiO2(Silicon dioxide) : 공기 중 매우 안정적이고 strong dielectric을 가짐. 온도 가열시 쉽게 자라는 특성 가짐.

- 높은 bandgap(1.12eV) : operating temperature가 높고 breakdown voltage가 높음.

- Vth = 0.7V로 상대적으로 높은 편.

기존에 Wafer로 사용했던 Ge(저마늄)과 비교해보자면,

- GeO2는 만들기 어렵고 물에 잘 녹으며 높은 온도를 잘 견디지 못함.

- Ge의 Vth=0.3V 정도로, leakage 문제가 발생할 수 있음.

과 같은 단점들에 비해 Si가 매우 좋은 특성을 가지고 있음을 알 수 있습니다.

- Crystal Lattice

갑자기 crystal lattice에 언급하는 이유는,

Si의 격자 특성에 따라 전기적인 특성이 바뀌게 되고 이러한 이론의 배경을 말하기 위해 추가하였습니다!

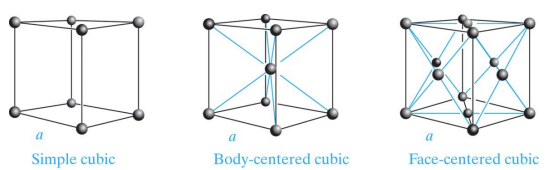

위 사진은 Cubic lattice로, 원자 구조의 기본 단위, unit cell을 보입니다.

이때, Facd-centered cubic(FCC)는 Si가 보이는 diamond structure의 기본 구조입니다.

그리고

α는 Lattice constant로 물질의 고유한 특징을 나타냅니다.

이후 배우게 될, epi-growth를 진행할 때 이 α값을 matching하는 것이 중요한 요소가 되겠습니다.

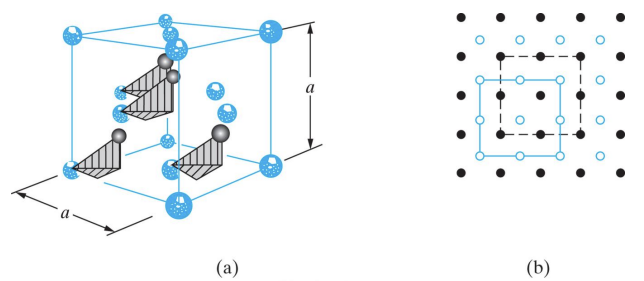

Diamond lattice에서 a/4+b/4+c/4에 위치한 atom이 어떤 물질인지에 따라 구조의 명칭이 달라지게 됩니다.

다른 원자들과 같은 원자라면 Diamond structure로, Si, C와 같은 물질의 구조를 말합니다.

반대로 다른 원자가 이 곳에 놓여있다면, Zinc Blende structure로, GaAs와 같은 물질의 구조가 됩니다.

다음과 같은 crystal plane은 3가지 종류가 있고, 각각은 다른 저항도를 가집니다.

저항이 바뀌면서 전기적 특성이 바뀌면서 Si의 특성도 바뀌는 것이 됩니다.

그리고 이러한 구조에서는 Defect를 가질 수 있는데,

이러한 defect들로 인해 불안정한 구조가 형성되면, 원치 않는 작동을 하게 될 수 있습니다.

왼쪽은 point defect들로,

ⅰ vaccancy ; 빈공간

ⅱ interstitial ; 원자들 사이에 껴있는 것

ⅲ substitial ; 기존 원자와 교체되어 있는 것

ⅳ Frenkel defects ; 물리적으로 결합이 되어 있는 것

과 같은 종류를 가집니다.

오른쪽의 linear defect는 dege, disloaction과 같이 epi-growth에서 α가 맞지 않을 때 자주 발생합니다.

< Wafer 형성 >

- From Sand to Ingot

sand 형태의 Si를 Ingot으로 형성하는 과정은 다음과 같습니다.

① Sand

- 높은 purity를 위해 여러번 가열해 불순물을 없애는 과정 진행

② MGS(Metallic Grade Silicon)

- 금속들이 포함된 형태, ~1800℃의 고온에 존재

- 전기적으로 사용하기에 적합하지 않음

③ EGS(Electronic Grade Silicon)

- 불순물을 걸러내기 위해 gas를 주입

- HCl로 MGS 정제, H2를 통해 정제 중 생긴 물질 제거해 전기적으로 사용할 수 있는 Si(EGS) 형성

- Ingot 제작 방법

Ingot은 wafer를 만들기 위해 형성하는 Si 기둥과 같은 형태의 물질을 말합니다.

이러한 Ingot을 만드는 방법은 2가지 존재하는데, 둘의 방법과 장단점을 비교하여 알아두면 도움이 될 것 같네요.

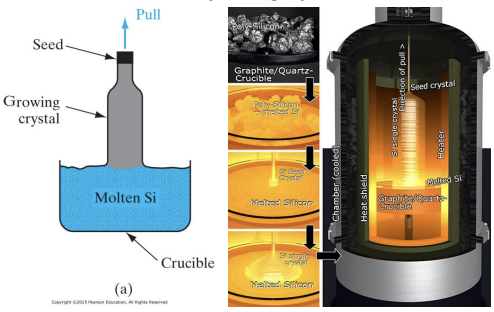

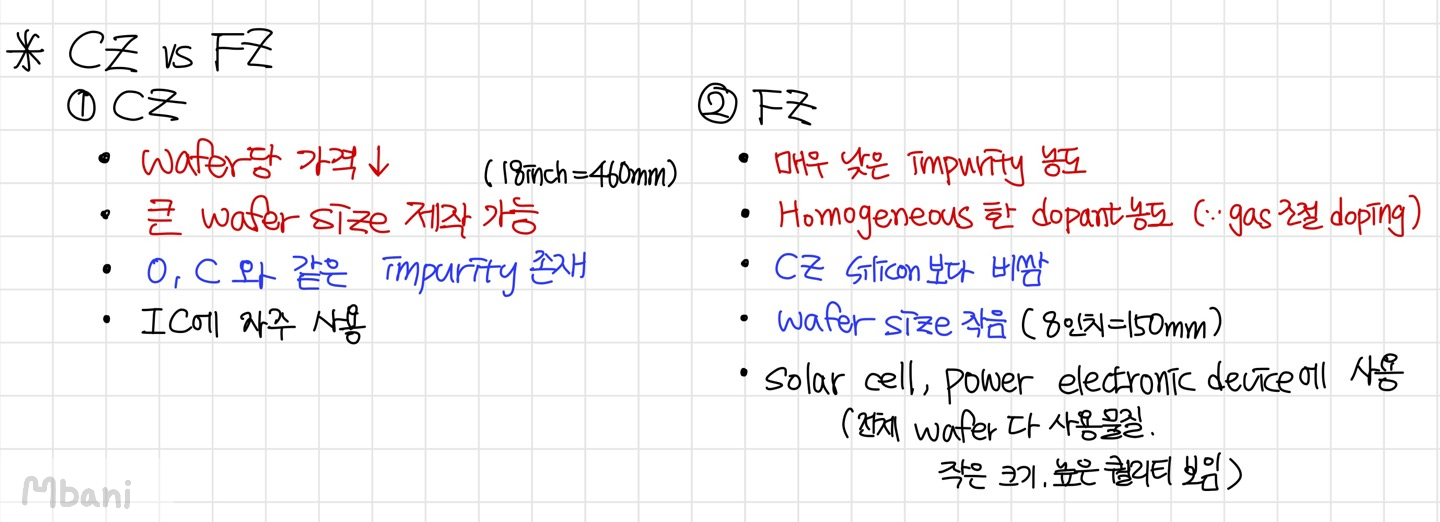

1) CZ(Czochralski) Method

- EGS를 Single-crystal Si로 바꾸어 Ingot 형성

ⅰ쪼갠 EGS를 cricible에 넣어 녹임

ⅱ seed가 아래에서 위로 회전하며 올라오면 Si가 굳으며 올라옴

ⅲ seed crystal 방향에 따라 생성되는 ingot의 crystal이 바뀜. 보통 단결정, single crystalline으로.

- wafer의 diameter는 temperature와 pulling rate에 관여

- p/n type을 위한 dopant 추가는 녹인 상태에서 추가로 넣어줌

- IC 에서 사용함.

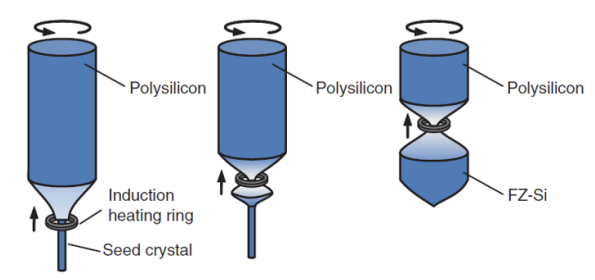

2) FZ(Float-Zone) Method

ⅰ polysilicon 형태를 가열된 RF ring이 통과하며 녹인 뒤 ring이 지나가면 다시 고체로 굳어짐

ⅱ RF ring에서는 액체상태. 이때 O와 C같은 impurity를 넣어줌

ⅲ RF ring을 통과한 Si는 FZ-Si로 단결정(mono crystalline)이 됨

- dopant는 RF ring 안에 있는 액체 상태일 때 dopant gas를 주입하여 넣어줌

- wafer 사이즈에 한계 존재

+ 둘의 장,단점 비교

- From Ingot to Wafer

이렇게 형성한 Ingot을 Wafer로 만들기 위해서는 다음과 같은 과정들을 거쳐야 합니다.

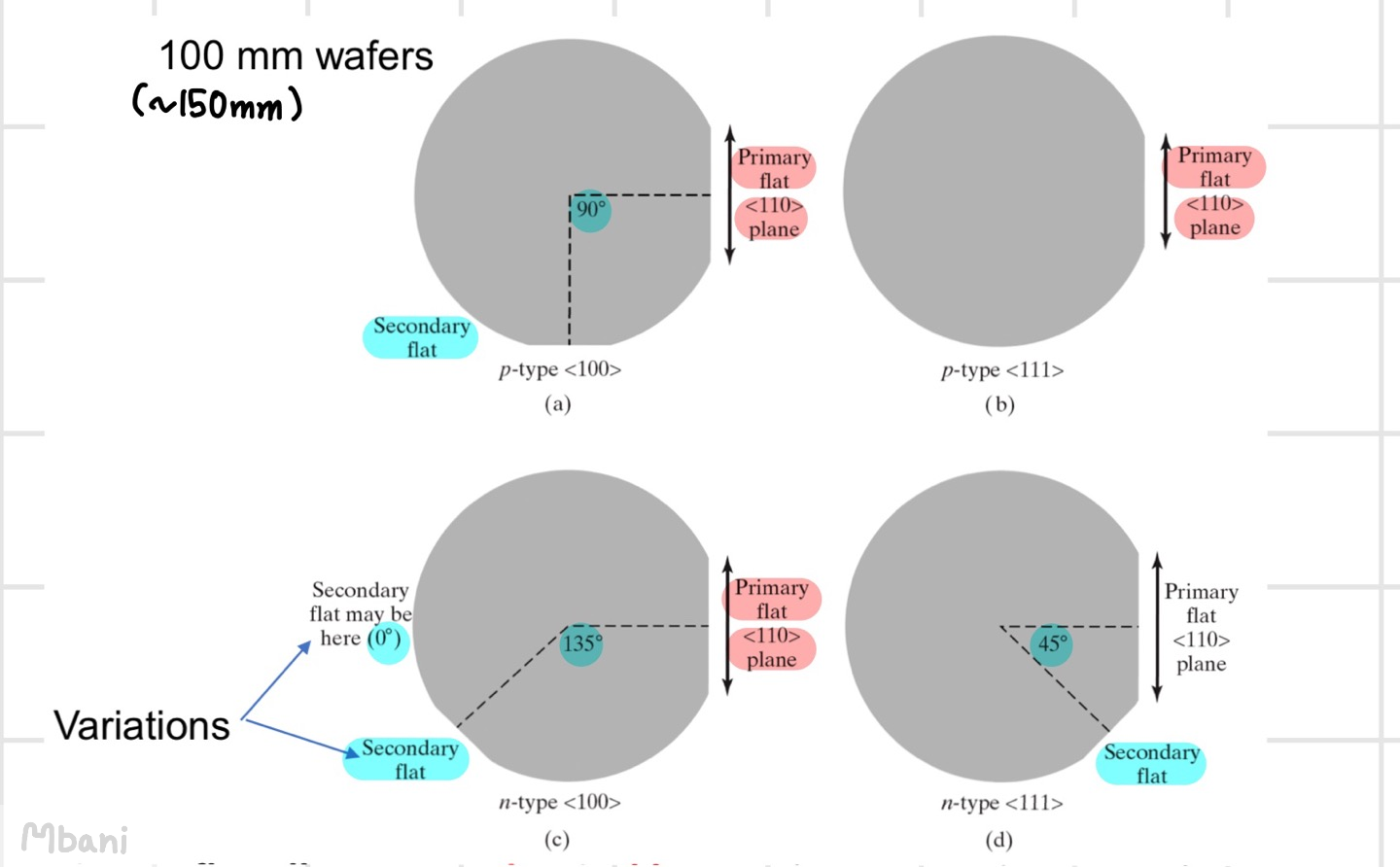

① grinding : extra diameter를 맞추기 위해 flat/notch를 자르는 과정.

- flat, notch : (100), (111)등의 식별코드를 표식으로 남겨둔 것

- standard flat을 따름.

② sawing(slicing) : single wafer를 만들기 위해 톱이나 다이아몬드 실로 자르는 과정

- Ingot의 결정성으로 인해 외부 충격에 약하기에 어느정도의 두께를 가지고 잘라야 함.

- wafer 사이즈가 증가할수록 자르는 두께 증가

③ Edge-rounding : wafer edge를 round하게 잘라주는 과정

- wafer의 높은 결정성이 외부 충격, 특히 특정한 방향에 대해 약한 특성을 가짐

=> 공정시 edge에 가해지는 충격을 보호하는 차원에서 이러한 공정 진행

④ Lapping : Al2O3, water, glycerin과 함께 물리적으로 돌려 깎는 과정

- 50um정도를 깎아내어 표면에 rms=2um정도의 거칠기를 가지게 됨.

⑤ Chemical etching : 화학적 반응을 일으켜 불순물을 없애는 과정

- 수용액에 wafer를 담구어 진행

- 표면 20~25um 정도를 제거함

3Si + 4NHO3 + 18HF → 3H2SiF6 + 4NO + 8H2O

· nitride acid(NHO3) : Si를 SiO2로 변환 (표면 아래도 같이 변화하며 Si 표면이 제거되며 contact impurity도 같이 제거)

· Hydrofluoric(HF) : SiO2 제거

· Acetic acid(CH3CHOOH) : reaction rate control

∴ 여러 impurity, particle이 존재하는 부분 전체를 SiO2로 변형함으로써 모든 불순물을 HF로 제거하게됨

=> pure Si wafer surface 형성

⑥ CMP(chemical Mechanical Polishing) : slurry를 도포해 압력과 회전을 가해 표면을 갈아주는 과정

- slurry는 NaOH에 있는 SiO2 particle입자의 suspension으로 구성됨

- 공정 중간중간 많이 사용

이외에도

- cleaning ; DI water

- Inspection ; 빛으로 검사

- particle counting ; defect 확인

- epitaxial growth ; 전기적 사용 준비

와 같은 과정을 진행합니다.

< Cleaning >

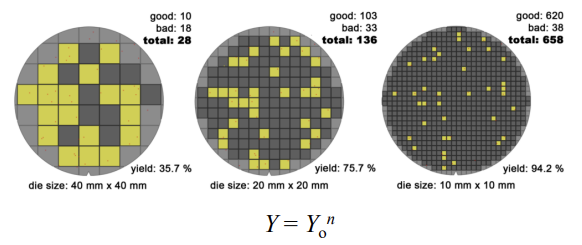

완성된 wafer는 cleaning과정이 필요합니다. wafer 수율과 직결되는 문제이기 때문에 중요한 과정으로 볼 수 있습니다.

- Cleanliness and Yield

Yield, 수율은 다음과 같은 식으로 구할 수 있습니다.

Yo는 한 번 수행할 때의 수율이고 n은 step의 횟수에 대한 미지수 입니다.

99%의 수율 과정은 100번 진행하면 37%의 수율, 500번 진행하면 0.66%의 수율이 되기 때문에,

최종적인 수율을 잘 control하는 것이 가장 중요하겠습니다.

이러한 수율에 영향을 미치는 particle들을 없애기 위해, 공정을 clean room에서 진행합니다.

particle, contamination control이 가장 중요하기 때문에 HEPA filter를 사용해 공기를 순환시켜 이들을 제거합니다.

이때 사용하는 단위 class는 1, 10, 100과 같은 class는 1ft^3에 존재하는 0.5um보다 작은 particle의 갯수를 말합니다.

오염을 시키는 contamination의 종류를 간단히 정리하면 다음과 같습니다.

1) 주요 contamination

- deposition chamber wall을 통한 박막 flacking (chamber의 문잉 여닫힐 때 나오는 물질들로 인한 오염)

- wet bench로 인한 증기 오염

2) 공정 시 사용하는 물질의 순도(purity)

- 물질의 순도. 3N 물질(99.999%)에서 0.001%의 impurity의 영향은 갯수가 많을수록 커짐.

- 물질이 요구하는 순도는 5N(99.99999%)~7N(99.9999999%)

- Cleaning 방법

Cleaning 하는 방법은 다음과 같이 분류할 수 있습니다.

① Wet Cleaning

- DI(deionized) water로 초음파 세척을 진행하여 이온화 된 물질을 제거.

- 높은 효율을 보임. (good purified, filtered)

- wet bench에 사용하는 화학물질 자주 교체 필요, 증기 방출로 오염될 수 있음.

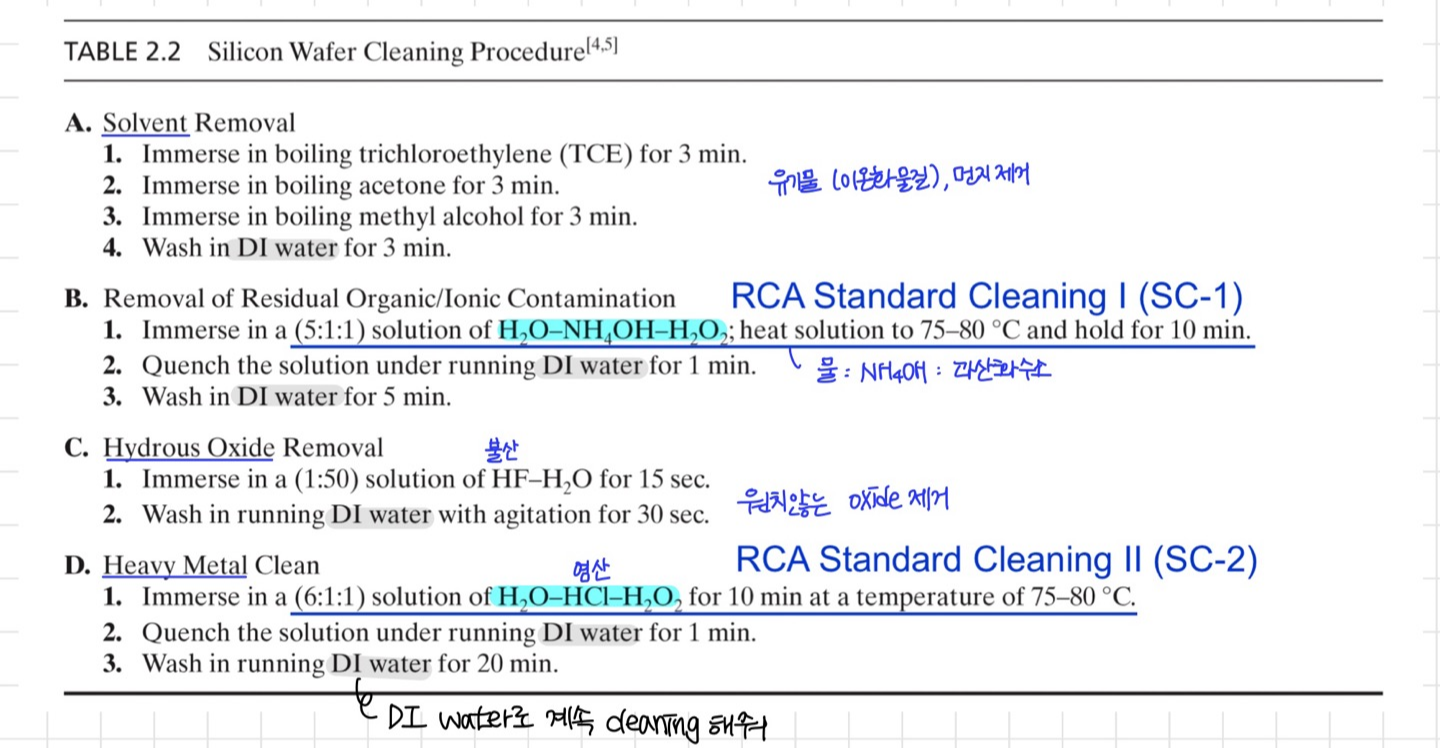

② RCA Cleaning

- standard cheaning 절차에 따라 진행.

- 각 과정이 끝나고 DI water로 cleaning하는 과정이 있음.

③ Dry Cleaning

- gas, vapor, plasma 등을 이용한 cleaning.

- 공정 중 자주 사용 가능하고 여러 과정에 걸쳐 같이 쓰기 용이.

- 표면에 가해지는 영향이 없어, surface tension effect가 없고 dry도 필요 없음.

- UV ozone과 oxygen plama로 organic물질을 씻겨 나가게 특성을 변화시킴.

(UV Cl2 : metal 제거, HF vapor : native oxide 제거)

오늘의 글은 여기까지 입니다!

다음은 Photolithography에 관한 내용으로, 조금 긴 분량을 가지고 올 것 같아요!

부족한 글 읽어주셔서 감사합니다 :)