IDEC에서 진행하는 광운대 강좌가 여석이 있길래 바로 신청했습니다.

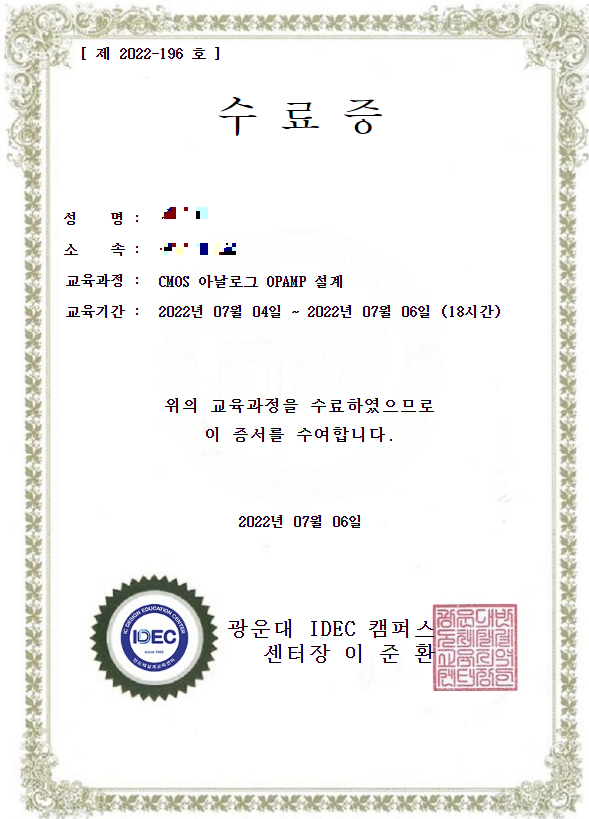

2022.07.04~07.06, 3일동안 대면으로 진행하였고 매일 6시간 씩 18시간 수강하였습니다.

~1일차~

<PN Junction>

CMOS의 내용에 들어가기 이전, 기초적인 device physics에 대한 이야기를 진행했습니다.

equilibrium 상태의 PN junction에서

p-type에는 3가 원소, n-type에는 5가 원소의 불순물을 intrinsic Si에 doping하여 제작하게 됩니다.

p-type에서 보이는 hole은 개념적인 것일 뿐, 실제로는 전자가 하나 없는 상황이 됩니다.

즉, 전자를 받기 쉬운 물질이라고 생각하면 됩니다.

그리고 built-in potential=0.7V로 쓰이지만, 농도에 따라 다르게 변합니다.

<MOS Capacitor>

MOSCAP은 gate-SiO2-Si의 형태로 주로 이루어 집니다.

<MOSFET>

MOSFET circuit modeling에서, V_SB는 source와 bulk사이의 전압을 말합니다.

이 bulk값은 V_T에 영향을 끼치기 때문에 여러개의 MOSFET이 연결되어 있을 때는 B를 분리해 설정하게 됩니다.

단일로 존재할 때도 B를 변화시키지 않게 하여 보통 우리가 아는 3 term의 상황에서 조절하게 됩니다.

Pinch-off는 다음과 같은 현상입니다.

<실습>

실습은 CADENCE Compeser를 이용하여 시뮬레이션을 진행하였습니다.

+ 지금까지 주로 PISpice를 이용하여 진행했는데, 처음 보는 툴이라 많이 서툴러 실습 때 진행이 조금 어려웠다는 점...

+ 첫 날에는 시뮬레이션 모델이 제대로 작동하지 않아 진행이 어려웠습니다...

<Amplifier Analysis(1)>

Small signal을 모델링 하기 위해서, saturation region의 다양한 paramater와 analysis를 알아야 했습니다.

추가적으로 design oriented를 배웠습니다.

1. Analysis의 목적은 회로 설계의 이해이며 수식이 아니다.

2. detail에 대해서는 시뮬레이터를 이용하면 된다.

3. 수식을 단순화 하고 복잡함을 피해라(주로 level-1의 단순 모델을 이용해 분석)

Amplifier analysis는 전자회로수업에서 배웠어서 간단히 복습하는 시간을 가졌습니다.

~2일차~

2일차 부터는 수업이 정말 이해가 안가서.. 필기들로 대체하겠습니다 ㅠㅠ.. 흑흑

<Amplifier Analysis>

<Differential Amplifier>

2일차부터는 실습 진행이 잦았습니다.. 성공률 50%정도..ㅜㅜㅎ ... ..ㅎ

~3일차~

<Current Mirror>

<Feedback>

전체적인 후기))

실습과 이론을 번갈아 가며 진행하였는데 저에게는 진행 속도가 빨라서 따라잡지 못한 점이 아쉬움으로 남습니다.

근데 다들 저 빼고 다 진행하신 것 같아 수업이 끝난 후 교수님께 따로 질문도 드리고 쉬는시간도 활용해 봤지만..

전체적으로 전자회로에 대한 내용 복습과, 디지털 집적회로에 대한 내용 예습을 한 것 같아 나름 기억에 남습니다.

그래도 퀴즈 열심히 풀어서 수료했습니다 브이 V( '^' )V

늦은 IDEC 후기였습니다!