안녕하세요!

이번 게시글은 ion implantation에 대해 이야기 해보려 합니다.

이번에도 수식이 조금 있어서 그부분은 필기로 대체하고, 정리할 수 있는건 타이핑해서 최대한 정리해 보겠습니다!!

< Impurity Doping >

diffusion에 이어 ion implantation도 impurity doping의 한 방법입니다.

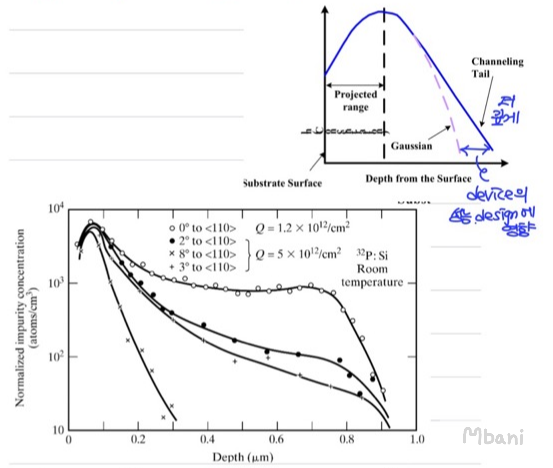

위 그림과 같이 가속화된 dopant를 넣어주고, 일정 깊이에서 최대 농도를 가지는, Gaussian 분포를 가집니다.

< Ion Implantation >

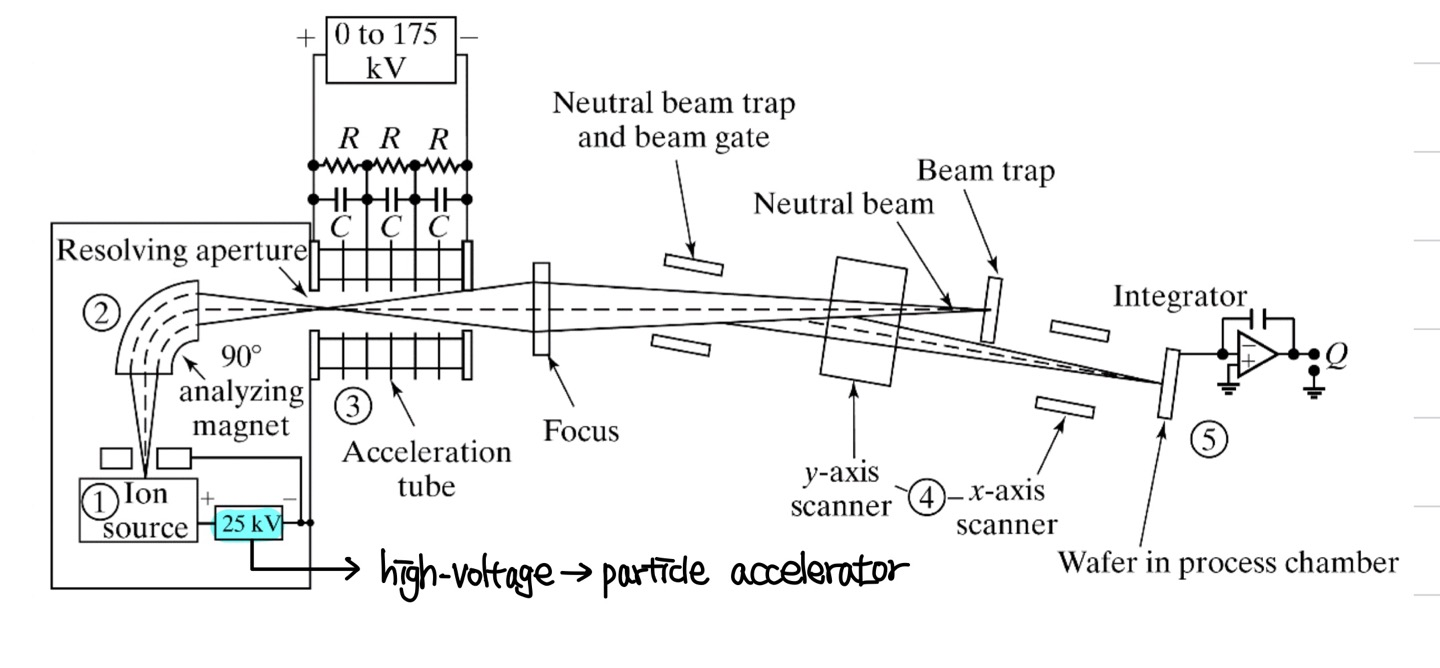

- Ion Implanter - High voltage Particle Accelerator

위는 ion implantation을 진행하는 implanter입니다. 각 번호로 매겨진 부분에 대해 이야기 해보겠습니다.

① Ion source

high voltage(25kV)에서 동작하는 ion source는 원하는 이온 포함된 gas가 주입되어 있습니다.

강한 V로 인해 plasma형태로 변화되는데, plasma는 기체성질을 띄고 반응성이 높으며 쉽게 이온화 됩니다.

이로인해 여러 이온들이 형성됩니다.

② Mass spectrometer(mass analysis)

자기장을 걸어 전류를 발생시켜 힘, Forse를 만들어 냅니다.

그리고 투입된 이온들은 mass에 따라 경로가 휘게 되고 원하는 이온만 통과하게 만듭니다.

자기장(magnetic field)과 원심력(centrifugal force)이 같아질 때 진행되고, field를 조절해 원하는 mass의 이온만 통과하게 합니다.

③ High-voltage accelerator

통과한 이온들을 가속화 시켜 implant되게 합니다.

④ Scanning system

주입된 이온의 수를 세 이온 주입의 진행을 파악

⑤ Target chamber

웨이퍼 장착해 이온주입을 진행

위 구조들을 통과하여 wafer에 이온들 주입하게 됩니다.

- Total dose Q

implanter를 이용해 total dose Q를 형성하게 됩니다.

ion implantation의 장점은

여러 doping농도를 형성 가능하고 원하는 depth를 정확한 형태로 정밀하고 방향성있게 형성할 수 있다는 점입니다.

아래 필기에서 Q의 식을 확인할 수 있습니다.

- Project Range and Straggle

projected ion range(Rp)는 원하는 깊이 지점을 말합니다. doping을 지점에 얼마나 할 것인지 최대 지점을 말합니다.

그리고 straggle은 ΔRp와 ΔRㅗ로 각각 수평방향과 수직방향의 오차를 말합니다.

위 필기의 그림을 보면, 위 오차들을 확인할 수 있습니다.

multiple collision(여러번 부딛히며 더 깊게 doping되는 현상)과

channeling(고에너지로 인해 Si 사이를 통과해 더 깊게 doping) 두 현상이 다음 오차를 발생시킵니다.

LSS theory를 이용하면 위 값들을 계산할 수 있습니다.

- Selective Implantation

ion implantation을 막는 mask meterial이 존재합니다.

[ SiO2(1) / Si3N4(0.85) / PR(1.8) ]

Si3N4는 주로 pad oxide로 사용되는데, hard mask로 침투가 잘 안되는 성질을 가집니다.

각 물질 옆 괄호 안 숫자는 Rp의 얼마만큼이 mask동작을 하는지를 말하고 이 값을 곱한만큼의 값만큼의 물질이 필요하다는 의미입니다.

이 값들 또한 계산을 이용해 minimum mask thickness를 구할 수 있습니다.

- Junction Depth

junction depth는 x_j로 나타내고 doping농도와 background 농도가 같은 곳의 깊이를 말합니다.

이 또한 아래 식을 통해 구할 수 있습니다.

- Channeling

정렬된 Si atom에는 crystal에 open space로 존재하고 있습니다.

들어오는 ion flux의 각도가 Si atom과 부딪히지 않게 들어가면, channeling effect가 발생하며 더 싶은 doping process를 형성하게 되는 것입니다.

ion channeling은 undesired dopant profile인 tail을 형성하게 됩니다.

이를 줄이기 위해 tilt(기울기)를 가지고 wafer에 doping을 시키면 되는데, 이 방법을 사용하면 shadowing effect가 발생합니다.

또 이를 해결하기 위해 post-implantation annealing을 진행하게 됩니다.

- Lattice Damage and Annealing

ion implantation을 진행하면 damage 영역이 생깁니다. 이를 해결하기 위해 annealing을 사용합니다.

annealing은 damage 영역을 recovery하고 electrical activation을 진행시키고 구조 정렬도 진행됩니다.

- Shallow implantation

ion implantation의 가장 큰 장점은 shallow implantation이라고 할 수 있습니다.

low energy와 rapid thermal annealing을 진행하면 얇은 junction, shallow junction을 만들 수 있습니다.

추가적인 개념으로 TED(Transient Enhanced Diffusion) 는 Si에 damage를 주면 일시적으로 5-10배 정도 diffusion coefficient가 증가하게 되어 온도에 대해 더 깊게 진행될 수 있습니다.

이는 tail의 문제를 야기하는 특이한 케이스 중에 하나입니다.

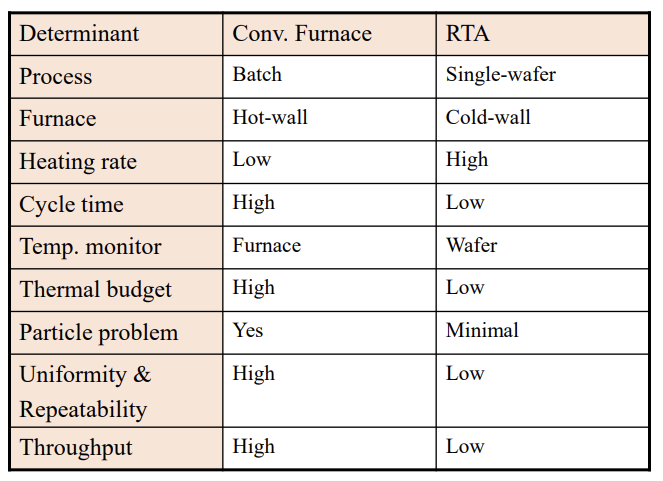

- RTA( Rapid Thermal Annealing )

RTA는 빠른 열 annealing과정입니다.

rapid heating을 가해 빠르게 진행하고 몇 초에서 최대 몇분까지의 짧은 시간을 진행합니다.

950-1050℃ 정도의 온도에서 50℃ /sec정도로 진행하고, 매우 낮은 Dt를 사용하기에 thermal budget에 큰 영향이 적습니다.

그렇기에

channel에 원하는 profile을 형성하는 적합

한 방법으로 사용됩니다.

아래 표는 RTA와 일반적 Furnace 과정을 비교한 표 입니다.

< Ion Implantation for CMOS fabrication >

이러한 Ion Implantation은 CMOS 소자에서 어떻게 활용되는지 확인해봅시다.

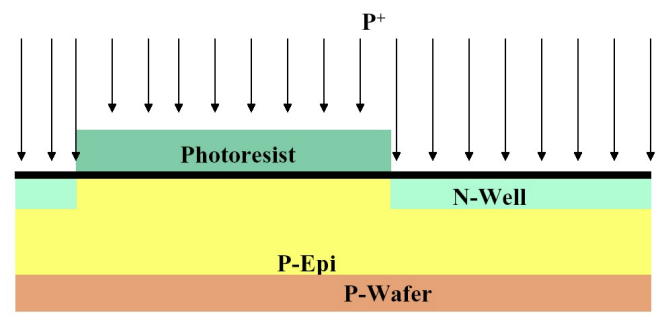

① Well formation

device 작동 영역을 만들 때 사용합니다.

높은 energy의 ion implantation을 진행하여 deep junction을 형성하게 됩니다.

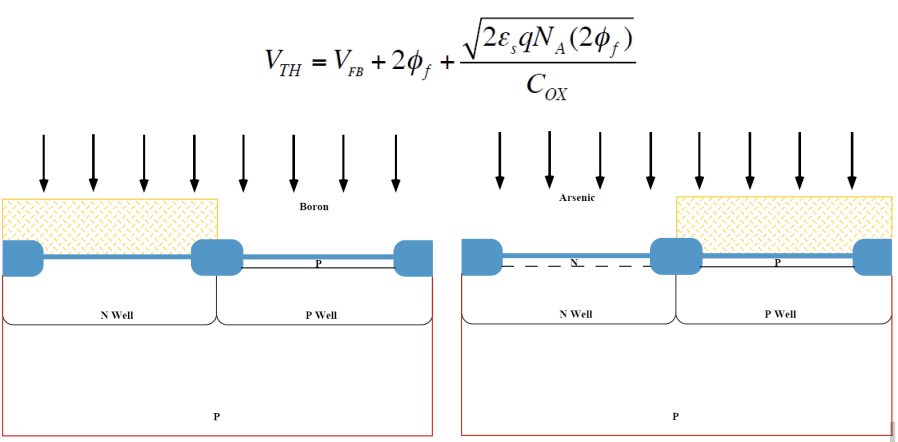

② Vth adjustment

Vth는 소자의 동작중 가장 중요한 parameter입니다.

이를 지정하기 위해 N_A를 지정하여 원하는 threshold voltage를 설정할 수 있습니다.

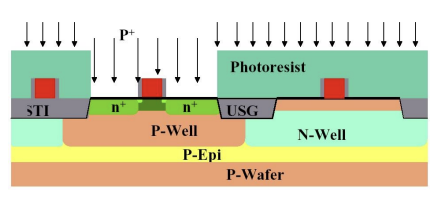

③ LDD formation

소자가 scaling이 되면서 Short channel effect로 Vth가 변하게 됩니다.

L이 너무 작아짐으로 인해 E(=V/L)가 너무 증가하게 되면서 hot carrier effect가 발생하게됩니다.

이러한 현상을 막기 위해 Source와 Drain 사이 영역에 doping이 덜 된 영역을 형성한 것이 바로 LDD입니다.

④ Source/Drain formation

소자에서 무조건적으로 필요한 부분입니다.

고농도로 highly doping(e20~21/cm3)로 n+를 위해 As, p+를 위해 B/BF2를 주입합니다.

Source와 Drain을 형성할 때 고려해야할 주요 parameter는 다음과 같습니다.

ⅰ. junction depth : SCE의 현상 중 하나인 punch through를 최소화

ⅱ. Rs : device performance의 degradation을 막아줌

여기까지 ion implantation 이었습니다.

생각보다 분량이 적은데, 다음 글인 thin film deposition부분이 조금 많을 것 같네요 허허

그래도 4개정도의 글 이후 반공 내용이 끝날 것 같습니다 하하

글 봐주셔서 감사합니닷 :)

'[학부 일기] 전자공학과 전공 > 반도체 공정 및 응용' 카테고리의 다른 글

| [반도체공정및응용] Etching (0) | 2023.03.01 |

|---|---|

| [반도체공정및응용] Deposition (0) | 2023.02.26 |

| [반도체공정및응용] Diffusion (0) | 2023.02.23 |

| [반도체공정및응용] Oxidation (0) | 2023.02.22 |

| [반도체공정및응용] Photolithography (2) (0) | 2023.02.06 |