안녕하세요!!

지난 (1)편에 이어 photolithgraphy에 대해 이어서 정리해 보려 합니다.

2023.02.06 - [전자공학과 전공../반도체 공정 및 응용] - [반도체공정및응용] Photolithography (1)

[반도체공정및응용] Photolithography (1)

안녕하세요! 이번 글은 Photolithography에 대한 내용에 대해 작성해 보려 합니다! 이부분 강의가 2주분량...(61페이지)였어서 조금 길 것 같아요. 그래서 두 파트로 나누어 진행하려 합니다! 너무 길어

electronics-bani.tistory.com

이번에는 Resolution과 DOF에 관해 이야기 해보겠습니닷!

< Resolution과 DOF >

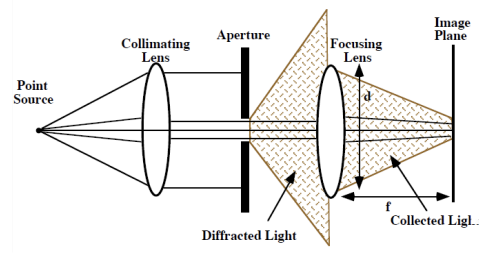

- Optics - Basic & Diffraction

resolution과 DOF를 알아보기 전, optic의 기본과 회절에 대해 알아보겠습니다.

dimension과 mask의 구멍 크기가 작아지면, 빛의 회절은 더욱 심하게 발생합니다.

mask의 구멍이 λ만큼 작아지면, 빛의 분산도 증가하게 됩니다.

원하는 image plane이 mask를 통과하면, lens를 이용해 다시 모아야 하는데, 렌즈의 바깥 정보는 사라지게 됩니다.

하지만 이러한 정보를 위해 lens를 키우기에는 한계가 존재합니다.

즉 원하는 이상적 상황은 λ→0, f→0 or d→∞에서 point image가 발생합니다.

- Resolution and Depth of Focus(DOF)

본격적으로 resolution과 DOF에 대해 이야기 해봅시다!

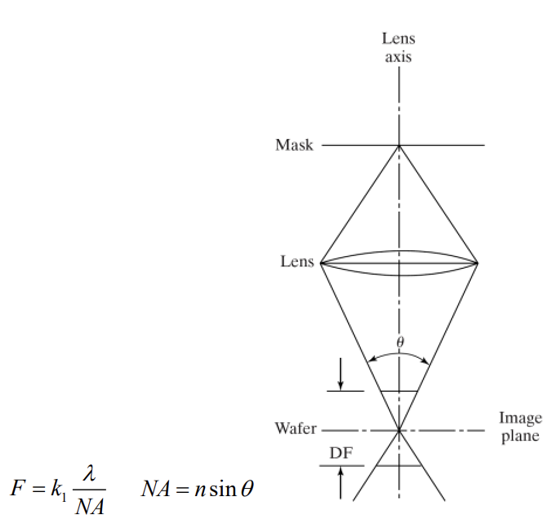

우선, Resolution, R은 pattern 사이의 최소 거리( = minimum feature size F )라고 말할 수 있습니다.

위 식에서 k1=공정상수, λ=빛의 파장(wavelength), NA=렌즈관련 값 입니다.

그리고 NA는 매질의 굴절률 n과 각도 θ의 사인값의 곱으로 나타낼 수 있습니다.

F를 최소한으로 만들기 위해서는, k1과 λ를 줄이고, NA를 증가시켜야 합니다.

DOF(Depth of Focus)는 PR의 두께로써, 빛이 PR에 얼마나 깊게 들어갈 수 있는지를 말합니다.

그러므로 DOF가 두꺼울수록 좋고 일정 수준을 확보해야 합니다.

위와 같은 식을 통해 DOF를 적당히 키우기 위해서는 k2와 λ를 증가시키고, NA를 작게 해야합니다.

즉, F와 DOF는 trade off관계이기 때문에, 일정수준 control이 필요하다는 것을 보여줍니다.

- Resolution을 향상시키는 방법들

이러한 Resolution을 향상시키기 위해서는 위에서 말했듯 3가지 방법이 존재합니다.

① NA 늘리기

② λ 줄이기

③ k1 줄이기

위 세가지 방법의 구체적 방법에 대해 자세히 알아보도록 하겠습니다!

1. NA 증가시키기

- Immersion Lithography

lens와 wafer사이에는 원래 공기가 존재합니다.

이때 존재하는 공기 대신 DI water를 넣어줌으로써 NA를 증가시키는 방법이 있습니다.

위의 수식과 같이 기존의 n_air(=1)보다 n_water는 더욱 큰 값을 가집니다.

이로인해 NA가 증가하면서 resolution을 증가시킬 수 있습니다.

다만 이 방법은

water를 유지하기 어렵고, wafer 위 불순물이 존재하며 비싸다는 단점들로 인해 실제로는 사용하지 않습니다.

2. λ 줄이기

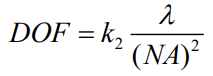

- Extreme-Ultraviolet (EUV) Lithography

EUV wavelength = 13.5nm에서 lithography를 진행함으로써 λ를 줄일 수 있습니다.

λ가 작기 때문에 매우 큰 에너지를 가지게 되고 이를 줄이기 위해 반사를 여러번 시켜 에너지를 줄입니다.

strong absorption문제를 해결하기 위해 reflective mask(반사 마스크)를 사용하는 것이죠.

물질이 흡수될 수 있기 때문에 진공상태에서 진행하고, mask의 크기가 작다는 특징을 가집니다.

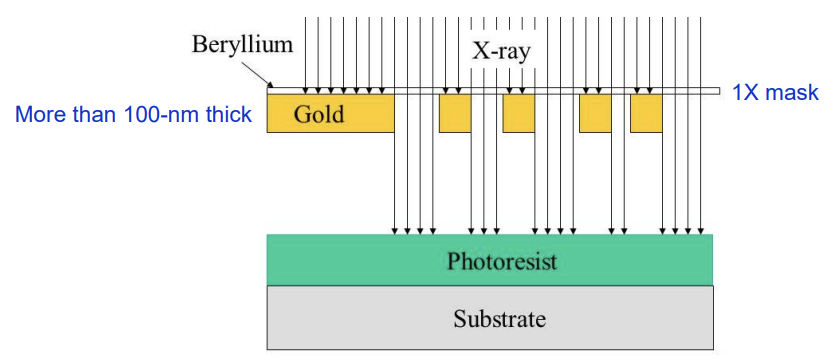

- X-ray Lithography

X-ray wavelength < 5nm 에서 lithography를 진행하여 λ를 줄입니다.

이 방법의 장점은 diffraction, 굴절이 없다는 것이고,

단점은 1) X-ray가 통과하지 않는 특수물질(금, Beryllium)으로 mask를 만들어야 하기에 어려움이 있음

2) single wavelength를 가진 X-ray source를 만들기 어렵고 비싸다는 점이 존재합니다.

- Electron Beam Lithography (EBL)

photomask의 pattern을 만드는데 주로 사용합니다.

큰 에너지로 지엽적인 노광을 하여 resolution을 높일 수 있습니다.

하지만 낮은 throughput을 가진다는 단점이 존재합니다.

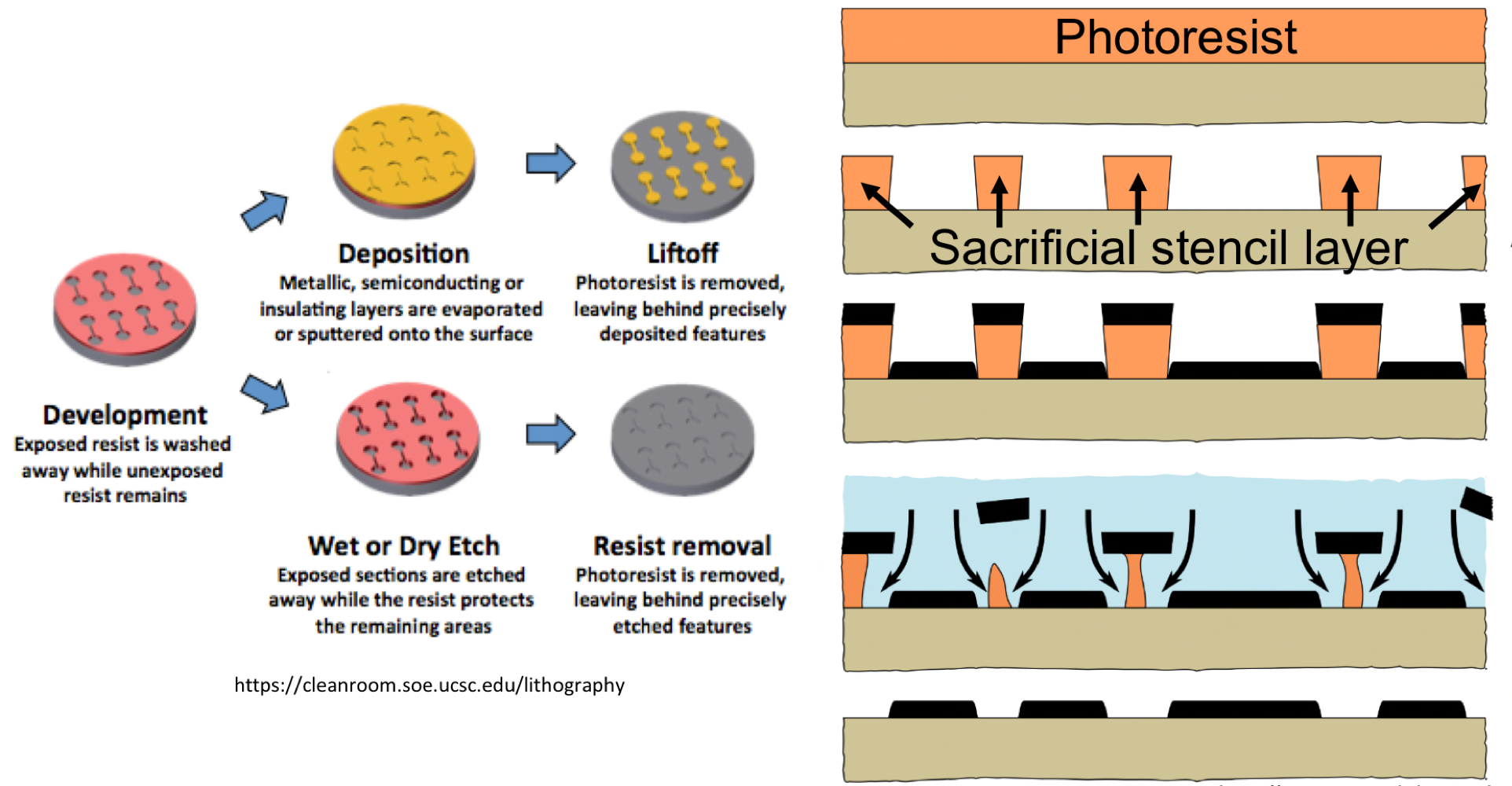

( + Stencil Lithography (without PR)

stencil 기법으로 patterning을 진행하면

resolution이 낮아지고 mask를 직접 contact하기에 direct patterning으로 진행하는 단점들을 가집니다. )

- Lift-off Process

PR coating과 development 후 Au(금)를 wafer 전면에 deposit한 뒤 PR을 strip하여 patterning하는 과정입니다.

etching을 하고싶지 않을 때 사용할 수 있다는 큰 장점과 꽤나 높은 resolution, 상대적으로 저렴하다는 특징을 가집니다.

다만 Lift-off ear(rabbit ear)가 PR 귀퉁이에 생길 수 있기에 유의해야 합니다.

3. k1 줄이기

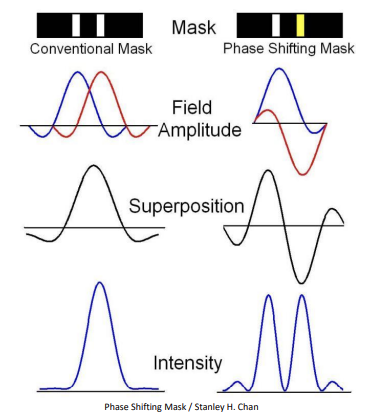

- Phase Shift Mask (PSM)

적당히 긴 λ의 빛이 작은 mask간격을 통과하면, 빛의 보강, 상쇄로 인해 원하는 pattern이 발생하지 않을 수 있습니다.

이를 해결하기 위해 PSM으로 phase를 180º 뒤집어 진행할 수 있습니다.

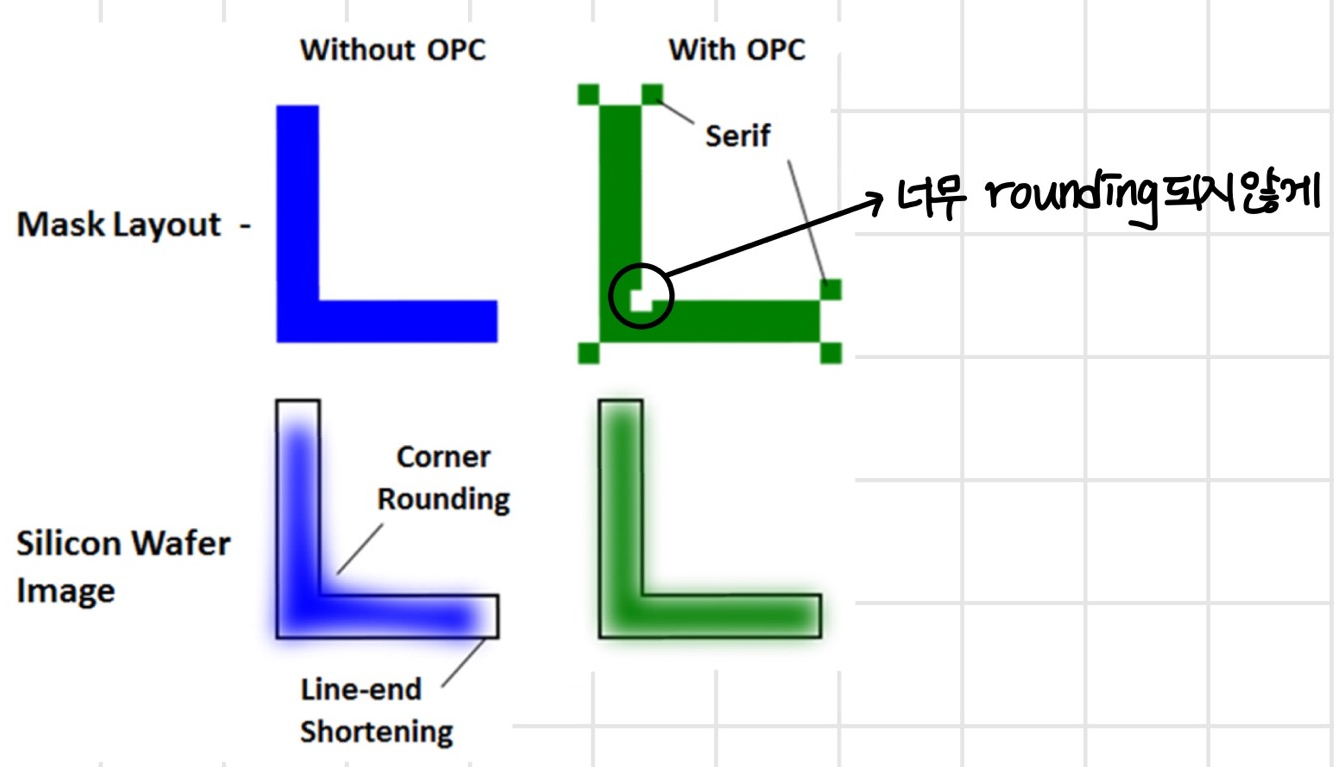

- OPC (Optical Proximity Correction)

layout에서 edge부분은 전사가 잘 되지 않습니다.

(∵ wavelength보다 feature size가 작아지면 빛의 회절이 증가해 원하는 pattern이 형성되지 않음)

이를 해결하기 위해 serif을 넣어 edge부분을 보상해 주는 방법입니다.

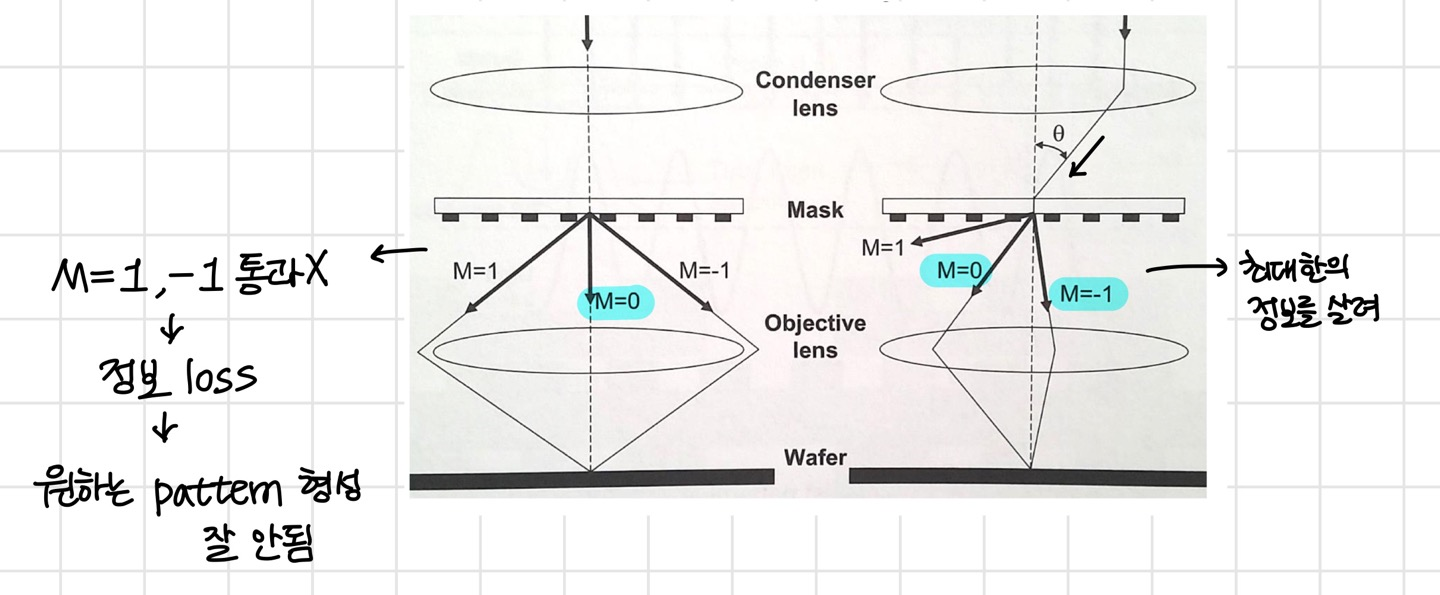

- Off-axis Illumination (OAI)

퍼지는 빛을 최대한 lens에 넣기 위해 빛이 들어가는 축을 약간 틀어서 인가하여 최대한의 정보를 살리는 방법입니다.

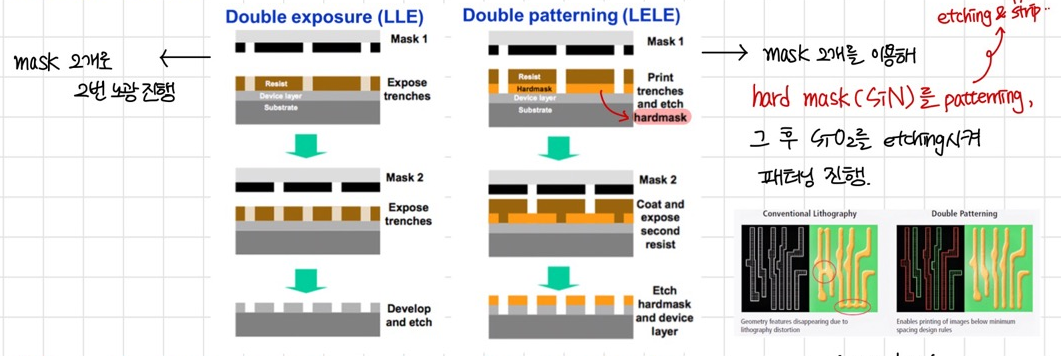

- LLE와 LELE

그림과 같이 LLE는 mask 2개로 2번 노광을 진행하여 더욱 촘촘한 pattern을 형성하는 방법이고,

LELE는 mask 2개로 hard mask(SiN)을 patterning한 뒤 SiO2를 etching시켜 patterning을 진행하는 방법입니다.

장점으로, mask를 한번 더 진행하기 때문에 resolution이 증가하고 step을 반복한다는 점이 있습니다.

반면 단점으로는, mask를 두번 사용하기에 많은 과정이 필요하므로 비용이 많이 들고, overlay issue가 발생할 수 있다는 점이 있습니다.

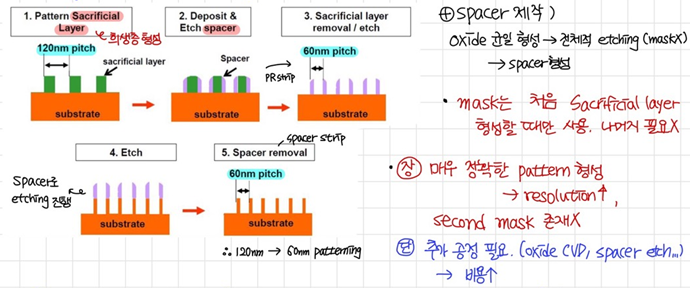

- Self-Aligned Double Patterning (SADP)

이 과정은 위와 같은 과정을 통해 patterning을 진행하는 것 입니다.

정리하자면,

희생층(sacrificial layer)형성 -> spacer 형성 -> 희생층 제거 -> 남은 spacer로 etching -> spacer strip

의 과정으로 기존 패터닝 공정보다 2배 얇은 패턴을 형성할 수 있습니다.

mask는 처음 희생층을 형성할 때만 사용하고, 매우 정확한 pattern을 형성하기에 resolution이 매우 높습니다.

- Self-Aligned Quadruple Patterning (SAQP)

SAQP는 SADP의 과정을 한번 더 진행하는 방법입니다.

SADP를 진행하고 한번 더 spacer를 형성하여 patterning하는 것입니다.

기존 패터닝 pitch보다 매우 감소된 값을 보임을 확인할 수 있습니다.

여기까지 photolithography 과정과 resolution을 증가시키는 방법들에 대해 확인해 보았습니다!

매우 긴 내용이여서 정리하는데도, 보는데에도 힘드네요ㅎ..

다음은 Oxidation에 대한 내용을 정리해 보겠습니다!!!

긴 글 읽어주셔서 감사합니다 :)

'[학부 일기] 전자공학과 전공 > 반도체 공정 및 응용' 카테고리의 다른 글

| [반도체공정및응용] Diffusion (0) | 2023.02.23 |

|---|---|

| [반도체공정및응용] Oxidation (0) | 2023.02.22 |

| [반도체공정및응용] Photolithography (1) (0) | 2023.02.06 |

| [반도체 공정 및 응용] Wafer&Cleaning (0) | 2023.01.09 |

| [반도체 공정 및 응용] CMOS Process Flow (0) | 2022.12.25 |