안녕하세요!

이번 반도체 소자 및 설계에서 다룰 내용은 Memory device에 대한 내용입니다!

메모리의 종류, 구조에 대해서 배우고

많이 사용되는 메모리인 DRAM과 FLASH 메모리에 대해 더 자세히 알아보려고 합니다!

- Memory

Memory는 크게 메모리 반도체, 시스템(비메모리) 반도체로 구분됩니다.

메모리 반도체는 휘발성(volatile) 메모리인 RAM(Random Access Memory)와 비휘발성(non-volatile) 메모리인 ROM(Read Only Memory)로 나누어 집니다.

이때 휘발성은 power가 있을 때만 데이터가 저장되는 물질을 말하고, 비휘발성은 power가 없어도 저장된 정보를 유지하는 특성을 말합니다.

RAM은 다양한 종류가 존재하지만, DRAM과 SRAM을 주로 말합니다.

DRAM은 빠른속도를 가지고(상대적) density가 높아 main memory로 주로 쓰이고,

SRAM은 매우 빠른속도를 가지면서 transistor를 많이 사용해 density가 낮기 때문에 cache memory로 많이 사용합니다.

현재 우리나라의 삼성, SK등에서 메모리 반도체 점유율이 D램은 70%, 낸드플래시는 50% 정도로 큰 비율을 차지하고 있습니다.

- Memory Architecture

- Memory Wafet Architecture

wafer는 두가지 영역으로 나누어져 있습니다.

동작을 수행하는 회로로 구성되어있는 chip영역,

chip을 구성하고 있는 단위 transistor를 넣어두어 wafer의 역할을 측정해낼 수 있는 test structures영역으로 말이죠.

test영역은 chip의 transistor를 측정하기에 어려움이 있기 때문에 생긴 영역이 되겠습니다.

wafer를 이용해 두가지 test를 할 수 있습니다.

① ET(Electrical Test)

test structure에서 나오는 data를 이용해 진행하는 test를 말합니다.

transistor의 정보에 대한 값을 알 수 있기 때문에, V_th, I_on, I_off, breakdown voltage등을 알 수 있습니다.

② EDS(Electrical Die Sorting)

main chip에서 주어지는 정보를 이용해 test를 진행합니다.

chip은 다양한 소자와 회로로 구성되어있기 때문에, 최종 회로 내에서 만들어지는 값들인

standby current, generated voltage 등을 확인할 수 있습니다.

(+standby current : 대기 전류 - 아무 상태도 아닐 때 흐르는 전류)

위 두 test를 통해 failure를 찾고 modeling을 진행할 수 있습니다.

예를들어,

fab-out된 wafer에 EDS를 진행했을 때, standby current가 fail되어 10%의 yield drop이 발생했다고 합니다.

이때 ET를 진행하니 off current가 매우 큰 것을 확인하였고,

S/D junction을 확인하였더니 Punch through가 발생한 것을 확인하였습니다.

이를 해결하기 위해 halo를 doping하거나 substrate의 도핑농도를 증가시켰고, 결론적으로 I_off를 줄일 수 있게됩니다.

이러한 매커니즘을 통해 발생한 문제를 해결할 수 있게되는 것 입니다.

- Memory Chip Archtecture

memory chip의 구조는 다음과 같습니다.

두 메모리 모두 'cell'과 'peri'영역으로 구성되어 있음을 확인할 수 있습니다.

우선 Peri(peripheral) 영역은 chip이 구동되는 곳으로, MOSFET으로 이루어져있습니다.

그리고 DRAM에서는 Cell, NAND flash에서는 Core라 불리는 영역은 data를 저장하는 공간입니다.

이때 DRAM은 1T-1C의 구조로 이루어져 있고, Flash는 1T로 이루어져 있습니다.

자세한건 뒤에서 자세히 다뤄보겠습니다!

- DRAM(Dynamic Random Access Memory)

- 단위

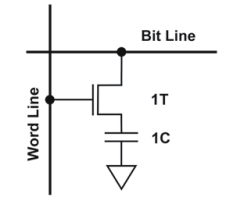

DRAM의 단위는 1T-1C로 이루어져 있습니다.

하나의 트랜지스터와 하나의 캡으로 capacitor에 charge를 저장하는 charge-based memory라고 합니다.

Q=CV에 의해 C가 큰 값을 가질수록 많은 전하를 저장할 수 있기에 큰 C값을 사용해야 합니다.

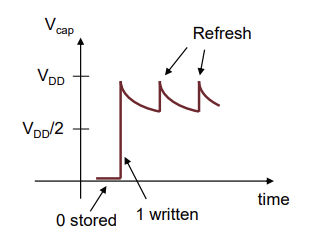

DRAM은 시간이 지날수록 캡의 전하가 빠져나가며 기존 상태를 잃게 됩니다.

이렇게 빠져나가는 상황을 junction leakage와 capacitance leakage라고 합니다.

그렇기 때문에 주기적으로 refresh를 해주어야 계속 값을 저장할 수 있습니다.

위 그림에서 WL(Word Line)은 read와 write를 switch해주는 역할을 하고, T의 gate에 연결됩니다.

BL(Bit Line)은 data를 옮겨주는 역할으로, drain에 연결되어 있습니다.

- 동작 원리

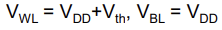

① Write '0'

V_BL에 GND를 연결해 주었기 때문에 전압차가 0V가 됩니다.

② Write '1'

V_BL에 V_DD만큼의 전압이 있기 때문에 생긴 전압차로 transistor에 전압차가 생기게 되고, capacitor에 전하를 저장할 수 있게 됩니다.

③ Read

V_BL에 V_DD/2의 전압을 precharge한 뒤, transistor를 킨 다음 amplifier로 증폭시킨 전압차를 비교합니다.

만약 0으로 쓰여있었다면, 전압차는 V_DD/2보다 작은 값이 측정될 것이고

1으로 쓰여있었다면, 전압차는 V_DD/2보다 큰 값이 측정될 것입니다.

위 사진을 보면, V_DD/2보다 큰 값에서 주기적으로 refresh되는 모습을 확인할 수 있습니다.

- DRAM Engineering

DRAM을 만들 때 scaling이 down되는 방향, 즉 density가 증가하는 방향으로 제작해야합니다.

이를 위해서 transistor와 capacitor를 이용하여 변경할 수 있습니다.

transistor의 scaling방법은 이전 게시글에 있습니다!

그리고 capacitor는 capacitance를 증가시키고 leakage current를 감소시키고, 면적을 줄이는 방향으로 해야합니다.

최소 크기의 메모리 셀은 다음 두가지 동작을 요구합니다.

1) data retention : 한 번 저장한 data를 유지하는 능력

C가 크면 같은 V에서 더 많은 Q를 저장할 수 있게되는데 이로인해 chrage leakage의 영향이 작아지게 됩니다.

예를들어 두 DRAM은 각각 10개 100개의 charge를 저장할 수 있을 때, leakage가 2개일 때 각각의 영향이 달라지게 되는 것입니다.

2) read operation : precharge로 값을 read할 때(sensing),

Q가 많을수록 V_DD/2의 범위가 커지기 때문에 정확한 operation이 가능합니다.

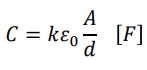

그러면 capacitance인 C를 증가시키는 방법에 대해 알아봅시다.

① Thickness(d) 줄이기

→ leakage current가 증가

② Dielectric constant(k) 키우기

→ high-k, hybrid 물질을 사용

→ band gap(Eg)가 감소 → band offset 감소 → leakage current 증가

③ Area(A) 키우기

→ 고르게 채우기 어려워 → 공정의 어려움

이렇게 capacitance를 증가시키는 방법은 다양하지만, 그만큼 단점또한 생깁니다.

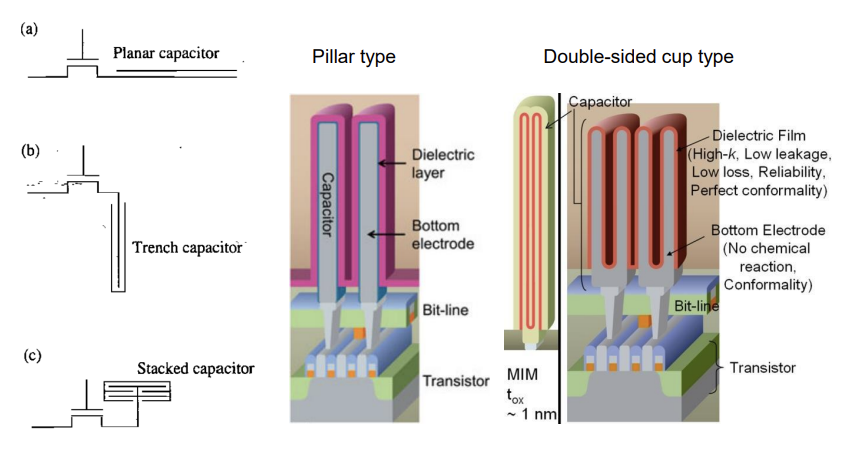

지금 C를 증가시키기 위한 구조들로는 아래 그림과 같은 것들이 있습니다.

순서대로 (a)는 planner capacitor로 A를 증가시켰지만, 차지하는 장소가 너무 커 비효율적인 단점이 있습니다.

그렇기에 다음과 같이 아래로 trench구조를 만들어 capacitor를 제작한 Trench capacitor,

위로 cap을 쌓은 Stacked capacitor가 있습니다.

현재는 Stacked capacitor를 많이 사용하고 있고 이들을 더욱 발전시킨 것이 오른족 두 그림입니다.

Pillar type은 원통형의 cap의 모습을 보입니다.

면적을 위로 올려 공정에 어려움이 존재하고,

너무 높게 올리게 되면 서로 붙거나, 쓰러지거나, 표면이 고르지 않은 등의 문제가 발생합니다.

Double-sided cup type는 Pillar type의 원통형 안쪽에도 insulator를 추가하여 전체 면적을 더욱 높인 형태를 말합니다.

- Flash Memory

- 단위

Flash memory의 단위는 1T로 간단한 구조를 보입니다.

FG 또는 CTL에 charge를 저장하고, Planer한 FG에서 3D CTF로 개발하고 있다고 합니다.

그리고 느리지만 높은 density를 보입니다.

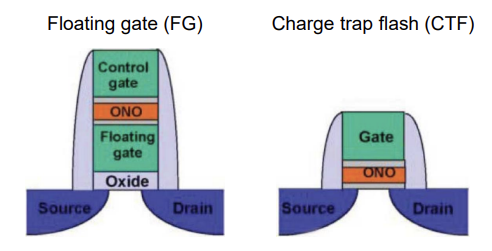

FG는 gate를 2개 가지고 있습니다. 반면 CTF는 gate가 1개이죠.

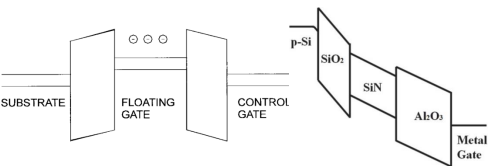

Control gate는 전압을 직접 연결하는 gate, Floating gate는 도체형태로 전압이 집적적으로 인가되지 않습니다.

사이의 ONO는 oxide-nitride-oxide로, 전하는 이곳을 통과하게 됩니다.

FG는 도체의 FG에 의해 SILC(stress induced leakage current)가 발생하고,

FG와 CTF 모두에서 leak path가 존재합니다.

두 EBD(energy band diagram)을 보면 각 물질의 접합부에서 band offset이 매우 크기 때문에

전하들이 쉽게 넘어가지 못해 장기간으로 정보를 저장할 수 있음을 알 수 있습니다.

charge들의 움직임은 tunneling을 통해 생깁니다.

다양한 tunneling이 존재하지만, 주로 FN tunneling으로 움직이게 됩니다.

그 외에도 Direct tunneling, TAT(trap assisteal tunneling) 도 일어나기도 합니다.

- 동작 원리

① Program

channel에서 tunneling oxide를 통해 floating gate로 FN tunneling하게 됩니다.

DRAM에서 writing과 같은 역할을 합니다.

② Erase

floating gate에서 tunneling oxide을 통해 channel로 FN tunneling하게 됩니다.

program과 반대의 역할을 합니다.

③ Read

cell transistor의 V_th를 이용해 값을 읽습니다.

위 그래프를 보면, READ voltage를 인가했을 때, Erase상태에서는 전류가 흐르고, Program상태에서는 전류가 흐르지 않습니다.

이렇게 READ voltage를 인가해 전류가 흐르는지 안흐르는지 판단함으로써 어떤 값이 저장되어 있는지 읽을 수 있습니다.

- density를 증가시키는 engineering

1. 3D NAND (V-NAND)

lateral scaling은 한계가 존재하고, 이를 cell-to-cell interface라고 합니다.

cell-to-cell interface는 transistor간의 간격이 감소하면서 원하는 transistor에만이 아닌 원치않는 옆 transistor에도 영향이 끼치는 현상을 말합니다.

이렇게 lateral한 방향으로 한계가 존재하면 vertical하게 stacking하게 됩니다.

그렇게 만들어진 구조가 3D NAND입니다.

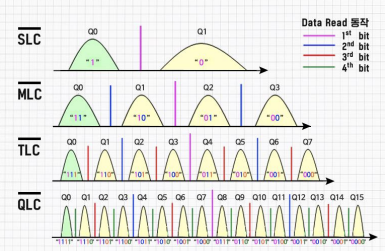

2. Multi-bit

멀티 비트는 하나의 transistor에 저장되는 bit수를 말합니다.

SLC : single level cell

MLC : multi level cell

TLC : triple level cell

QLC : quadruple level cell

저장되는 bit수가 증가할수록 저장을 더 많이 할 수 있기에 집적도가 높아집니다.

하지만, 안정성과 정확성이 떨어지고 간격 또한 줄어들게 됩니다.

현재는 TLC를 사용중이라고 합니다.

오늘 메모리에 관한 내용은 여기까지 입니다~

시험기간까지 달려보겠습니다.

달려라 치타!!!

부족한 글 봐주셔서 감사합니다.

'[학부 일기] 전자공학과 전공 > 반도체 소자 및 설계' 카테고리의 다른 글

| [반도체 소자 및 설계] Device Physics - Failure Analysis (0) | 2022.08.28 |

|---|---|

| [반도체 소자 및 설계] Device Physics - Display TFT (3) | 2022.05.29 |

| [반도체소자및설계] Device Physics - MOSFET Technology (0) | 2022.04.17 |

| [반도체소자및설계] Device Physics - scaling (2) | 2022.04.15 |

| [반도체소자및설계] Device Physics - MOSFET (1) | 2022.04.13 |