안녕하세요!!

오늘 반도체 소자 및 설계에서 다룰 내용은 scaling에 관한 내용입니다.

scaling으로 인해 생긴 Short Channel Effect에 대한 이야기를 중점으로 진행해보도록 하겠습니다.

- Transistor scaling

지금 만들어지고 있는 transistor는 speed와 density를 더 빠르게, 작게 하기 위해 계속 scaling이 일어나고 있습니다.

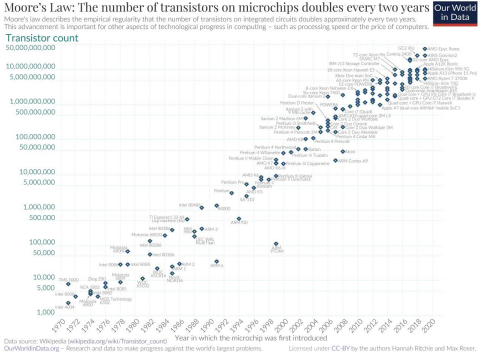

앞에서 언급은 안했지만, Moore's Law에 따라 2년이 지나면 transistor의 크기가 2배정도 감소함을 따르고,

그만큼 빠르게 발전하고 있음을 말하고 있습니다.

transistor의 속도는 RC의 값에 의해 제어됩니다.

빠른 속도를 위해서는 L을 줄이게 되는데, L이 감소하면

channel에 형성되는 resistance(R_ch)가 감소하게 되고,

gate area가 얇아지게 되면서 C_ox 또한 감소하게 됩니다.

R과 C가 모두 감소하기 때문에 RC delay는 작아지게 되고 switching time이 빨라지게 되는 것 입니다.

transistor의 면적은 gross die(net die) per wafer, wafer한 장당 나오는 chip의 총 갯수에 의해 정의됩니다.

더 작은 transistor를 만들기 위해 G/D(gross die) , N/D(net die)를 증가시키면 됩니다.

이렇게 transistor를 줄이게 되면 마냥 좋은 점만 생기는 것은 아닙니다.

크기가 감소하면 자연스럽게 channel의 길이인 L가 감소하게 되고, 이로인해 SCE(Short Channel Effect)가 발생합니다.

아래에서 6개 정도의 SCE에 대해 이야기 해보도록 하겠습니다.

추가적으로 이야기 하자면, MOSFET에서 V_th는 변하지 않고 일정한 값으로 유지되는 것이 좋은 동작이라 말합니다.

- Short-Channel Effect

1. Vth roll-off

channel length(L)이 감소하면서 depletion영역이 감소하게 됩니다.

그러면 depletion 영역에서 S/D의 영향이 이전보다 상대적으로 커지게 되고, gate의 controllable이 감소하게 됩니다.

이로인해 기존 V_th보다 작은 V_g에서도 MOSFET이 on되게 됩니다.

즉. V_th가 감소하게 되는데 이러한 현상을 V_th Roll-off라고 합니다.

(자세한 그림과 설명은 물리전자2 MOSFET내용에서 다뤘습니다!)

그러면, V_th의 변화는 얼마나 일어나는지 수식적으로 알아봅시다.

roll-off를 줄이는 것은 △V_th를 줄이는 방향이 되겠습니다.

- C_ox↑(t_ox↓ , k↑) : C_ox가 클수록 gate control이 쉬워지게 됩니다.

- W_d ↓ : depletion width를 얕게 하는, 즉 substrate doping농도를 증가시키면 변화가 작아집니다.

- r_j ↓: junction의 깊이를 얕게 하면 변화가 작아지게 됩니다.

이를 shallow junction이라 하고, 이를 만드는 방법은 [반소설]Fabrication Process에 나와있습니다.

이렇게 다양한 lateral한 parameter들로 V_th의 변화를 막을 수 있지만, 가장 좋은 것은 vertical한 방향으로 막는게 더 좋습니다. (SCE는 leteral한 방향으로 일어난 현상이기 때문)

vertical한 방향으로 scaling하는 것은 다음 게시글에 언급될 것 같네요!

2. Maximum E-Feild

channel의 길이가 짧아지면서 maximum E-field의 위치가 drain junction의 앞단에 걸리고,

이때의 E-field 값도 증가하는 현상을 maximum E-field라고 말합니다.

이 현상이 발생하는 이유는 두가지 정도로 설명할 수 있겠습니다.

첫번째, E=-dV/dx에 의해, drain 쪽의 potential이 급격하게 변했기 때문에, E-field도 증가하였다.

두번째, electron은 energy band diagram에서 potential의 경사가 더 클수록 빠르게 움직이기 때문에,

v_d = uE에 따라 E-field가 증가하였다.

결론적으로는, drain bias가 더 강할수록 더 큰 EBD 기울기가 생기기 때문에 max E-field가 증가하게 되는 것 입니다.

그러면 이렇게 증가한 maximum E-field로 인해 생기는 문제점이 SCE가 되겠죠?

이 종류에는 2가지가 존재합니다.

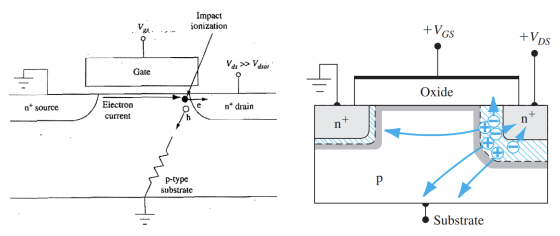

① hot carrier effect

hot carrier effect는 impact ionization에 의해 발생합니다.

impact ionization은 빨라진 carrier 때문에 다른 원자와의 충돌로 EHP가 새로 셩겨 carrier가 증가하게 되고, drain current가 갑작스럽게 증가하게 합니다.

이렇게 만들어진 EHP

- electron : gate oxide의 내부로 이동할 수 있을 정도로 에너지를 받게 됩니다. - damage, trap 형성

- hole : body로 이동해 substrate current가 될 수 있습니다.

이렇게 carrier는 각각 다른 경향을 보입니다.

여기서 SiO2에 injection된 electron은 oxide 내부에 damage를 입히고 trap을 형성하였기 때문에 channel에 생겨야 할 electron을 밀리게 합니다.

이로인해 V_th는 순간적으로 변하고, drain으로 흘러야 할 전자가 oxide에 들어갔기 때문에 drain current는 charge되지 않을 때 보다 감소, device의 수명도 감소하게 됩니다.

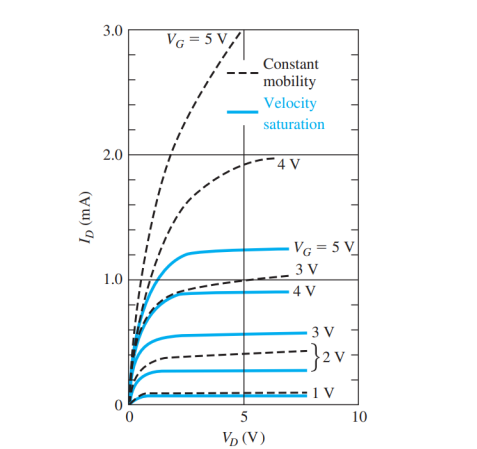

② velocity saturation

lateral scaling으로 인해 E-field가 증가했고 이 이유로 v_d = uE에 의해 E-field와 volocity는 linear한 관계를 가진다고 볼 수 있습니다.

원자와 충돌하면서 진행하던 carrier는 E-field가 매우 크게 증가하면 충돌할 때 잃어버리는 에너지가 커지게 됩니다.

이러한 scattering으로 E-field와 velocity는 큰 E-field에서는 더이상 linear하지 않고 saturation되게 됩니다.

이렇게 maximum E-field의 증가로 생기는 문제들을 해결하는 방법은 LDD를 추가하는 것 입니다.

LDD(Lightly Doped Drain)은 n+의 drain보다 도핑 농도가 낮은 n-의 물질으로,

이 물질로 인해 완만한 junction을 형성, E-field를 줄여주게 됩니다.

하지만 LDD는 n-의 낮은 doping농도로 인해 resistance가 커지기 때문에, drain current가 감소하는 문제점 또한 존재합니다.

3. DIBL(Drain Induced Barrier Lowering)

'디블', '디아이비엘'이라고 불는 DIBL은 long channel에서는 V_th에 독립적이던 V_d가

short channel에서는 영향을 끼치기 시작하는 현상입니다.

V_ds의 증가로 channel의 potential barrier height가 낮아지면서, V_th는 낮아지고, Subthreshold current는 증가합니다.

위 그래프를 통해 DIBL로 인해 낮아진 potential barrier를 확인할 수 있습니다.

그리고 roll-off와 비교를 해보자면,

DIBL은 drain voltage가 낮으면 거의 일어나지 않기 때문에 무시할 수 있지만,

V_ds가 높고 channel length가 짧으면 roll-off보다 DIBL이 더 심각하게 나타나게 됩니다.

4. Punchthrough

우리가 원하는 MOSFET의 동작은, channel 영역에서만 전류가 흐르는 상황입니다.

하지만, channel length가 짧아지면서 Source와 Drain의 depletion 영역이 channel아래에서 만나게 되면서

V_ds가 증가하게 되고, gate controllable이 감소하는 현상이 일어나게 됩니다.

결국 I_d또한 변화하게 되고 이러한 현상을 Punchthrough라고 합니다.

이 현상은 L이 짧아질수록 더 크게 일어나고, 원래는 saturation되는 전류가 이 영역에서는 증가하는 모습을 보입니다.

Punchthrough를 해결하기 위해서는 Halo(or pocket) 물질을 implant하면 됩니다.

halo를 substrate와 같은 종류에 doping농도가 더 높은 물질을 Source와 Drain영역에 붙여줌으로서

substrate doping이 강화되고, depletion width의 확장이 덜 되게 제어하는 역할을 합니다.

이렇게 halo를 넣어줬을 때,

L이 감소하면 halo영역이 inversion layer에 가하는 영향이 증가하면서 더 큰 gate voltage를 필요로 하게 되고,

최종적으로는 V_th가 증가하게 되는 현상을 reverse short-channel effect라고 합니다.

5. GIDL (Gate Induced Drain Leakage)

off 상태에서 drain영역의 valance band에서 conduction band로 electron이 흐르는 tunneling이 발생하게 됩니다.

이런 electron은 EHP가 생성되면서 leakage current가 발생하고, I_off가 증가하게 됩니다.

GIDL은 off current를 발생시키는 가장 큰 요인이고, V_GD가 작을수록 GIDL이 증가하게 됩니다.

6. Narrow Width Effect

Narrow Width Effect는 tansistor 각각을 고립되게 막아주는 방식에서 생기는 문제점을 말합니다.

이 현상에는 두가지 종류가 있습니다.

① LOCOS : narrow width effect (NWE)

gate oxide 두께가 증가하며 t_ox가 증가되는데, 이로 인해 Vth가 증가하는 현상을 말합니다.

그래프에서 W가 감소하면 V_th가 급격히 증가하는 경향을 볼 수 있습니다.

② STI : inverse narrow width effect (INWE)

STI로 분리하게 되면 gate가 평평하게 형성되는데,

edge 부분 추가적인 gate E-field를 더 받을 수 있게 되고, C_ox가 증가하게 되면서 V_th가 감소하게 됩니다.

오늘 내용은 여기까지입니다!!

다음은 MOSFET에서 사용되는 기술에 대해 정리할 예정이고, 중간고사 마지막 범위 입니다!

글 봐주셔서 감사합니다!!! :)♡

'[학부 일기] 전자공학과 전공 > 반도체 소자 및 설계' 카테고리의 다른 글

| [반도체소자및설계] Device Physics - Memory Device (0) | 2022.05.26 |

|---|---|

| [반도체소자및설계] Device Physics - MOSFET Technology (0) | 2022.04.17 |

| [반도체소자및설계] Device Physics - MOSFET (0) | 2022.04.13 |

| [반도체소자및설계] Device Physics - Resistance & Capacitance (1) | 2022.04.11 |

| [반도체소자및설계] Fabrication Process (0) | 2022.04.09 |