안녕하세요!! 이번에 새로 듣는 과목인 '반도체 소자 및 설계'에 대한 정리를 시작합니다!

중간고사 기간에 필기 정리를 한 뒤에 한번 더 줄글로 정리해 보겠습니다 '~'

이번 글은 'Fabrication Process'로, 물리전자2 처음에도 배웠던 내용입니다ㅎ

다음 학기에 배울 반도체 공정 수업에서 보다는 얕은 지식이지만!

열심히 한번 써보겠습니다..ㅎㅎㅠ

- MOSFET 복습

공정 과정을 알아보기 전에 공정하는 물질인 MOSFET에 대해 먼저 복습하고 넘어가봅시다!

MOSFET의 구조는 위와 같고, Metal Oxide Semiconductor Field Effect Transistor를 의미합니다.

이때 Metal Oxide Semiconductor 는 gate stack의 구조를 말하고,

Field Effect Transistors 는 전기장으로 transistor를 control함을 말합니다.

V_GS로 표기하는 gate voltage로 channel을 inversion시키는 종류에 따라

n-channel이 형성되면 NMOS, p-channel이 형성되면 PMOS라 말합니다.

channel에 흐르는 전류는 drift current로 인해 흐릅니다.

MOSFET의 type이 정해지면 전류에 기여하는 carrier는 하나로 정해지고, 이를 single carrier configuration이라 합니다.

NMOS는 electron이, PMOS에는 hole이 기여하는 캐리어가 되겠습니다.

MOSFET에서 가장 중요한 요소인 V_th(threshold voltage)를 기준으로 동작을 하고,

따라서 MOSFET은 전류의 ON과 OFF를 만들어 내는 switch역할을 하게 됩니다.

이때 on current와 off current는 서로 trade off관계를 가집니다.

MOSFET의 복습은 여기까지 하고, 이제 공정과정에 대해 알아보도록 하겠습니다

- Wafer

wafer는 주로 Si로 이루어진, 공정에서 사용하는 기판을 말합니다.

이 wafer를 만드는 방법 중 하나인 Czochralski Method는 용광로에 녹아있는 Si를 seed를 통해 올리고,

올라온 Si는 온도가 식으면서 굳게 되는데 이렇게 만들어진 ingot을 잘라서 wafer를 만드는 방법입니다.

이때 녹아있던 Si는 주기적인 구조가 모여있는 polysilicon상태였지만 굳은 Si는 주기적 lattice를 가진 crystalline으로 변하게 됩니다.

이렇게 만들어진 wafer는 우리가 ① 원하는 구조를 만들고,

② 원하는 성능을 내기 위해서 공정과정에서 발생한 impurity를 제거해야 합니다.

impurity는 위 두가지 목적을 달성하는데 심각한 문제를 야기하기 때문에 wafer를 cleaning해야 하고,

이 cleaning 방법은 3가지가 있습니다.

1. Clean room

이 방법은 wafer를 제작하는 환경 자체, chip fabrication자체를 깨끗하게 해주는 방식입니다.

위에서 아래로 바람을 주어 발생한 먼지들을 바람에 날려보내어 cleaning합니다.

clean room의 등급은 Class로 나타낼 수 있습니다.

예를 들어 Class 10은 cubic foot(한 변이 1ft인 정육면체)에 particle이 10개보다 덜 들어있는 상태의 등급을 말합니다.

이때 particle은 0.5um보다 작은 사이즈로 미세먼지와 초미세먼지와 비교못할 정도로 작은 값입니다.

Class는 1, 10, 100, ... 으로 정의되고, 일상은 Class 100,000정도, 요즘 사용하는 clean room은 Class 1정도라고 합니다.

2. Cleaning

Cleaning 방식은 wafer를 직접 깨끗하게 하는 과정입니다.

RCA cleaning이 보편적 과정이고,

액체상태의 용액을 이용하는 wet과 plasma, UV ozone, lase등을 사용하는 dry방식이 있습니다.

위에서 아래로 각 과정을 진행합니다.

Piranha과정은 고온에서 유기물을 제거하고 이 과정이 끝나면 얇은 SiO2박막이 형성되어 HF 과정에서 제거해 줍니다.

각 과정들 사이에는 DI(De-Ionized) water로 wafer를 세척해 줍니다.

3. Gettering

Gettering은 중요하지 않은 공간에 불순물을 넣어 impurity를 통제하는 방식입니다.

carrier는 얕게 형성된 영역에서 열 E를 받으면 쉽게 빠져나올 수 있습니다.

하지만 gettering 영역은 매우 깊게 형성되기 때문에 열을 가해도 넘지 못하고 capture되게 됩니다.

gettering방식에는 두가지가 있는데,

첫번째. Intrinsic gettering은 wafer 내에 존재하는 defect를 이용해 가두는 방식입니다.

Si 내부의 소량의 oxide나 Si 격자 구조의 defect에 가두게 됩니다.

두번째. Extrinsic gettering은 wafet아래의 절연막에 불순물을 넣는 방식이 되겠습니다.

- Oxidation

Oxidation은 silicon oxide박막을 형성하는 과정으로, gate 전류를 흐르지 못하게 하는 insulator를 만듭니다.

oxide물질은 resistivity가 높고 Energy band gap이 높으며 높은 E-field를 견딜 수 있습니다.

또한 Si와 SiO2 interface는 안정적이고 만들기 쉽고, dopnat의 확산을 막아줍니다.

이러한 Thermal oxide에는 두가지 종류가 있습니다.

Dry oxidation은 느리고 quality가 높고, Wet oxidation은 빠르고 quality가 높습니다.

위 그림은 oxidation이 일어난 Si wafer의 모습입니다. Si에 Reactant를 넣어 반응을 시켜 SiO2를 만들어 냅니다.

오른쪽 점선으로 표시된 Original Si surface와 현재 Si의 높이가 다른 것을 보아,

기존의 Si가 SiO2를 만드는데 0.46만큼 소진되었고, 이 Si로 1의 SiO2를 생성해 총 0.54만큼 두꺼워 졌음을 알 수 있습니다.

- Photolithography

이 과정은 빛을 이용해 원하는 패턴을 기판위에 찍어내는 공정을 말합니다.

이때 패턴을 만드는 물체는 Photoresist(PR)이라 하고, 빛에 의해 영향을 많이 받는 물질입니다.

PR로 가려지지 않은 부분이 없어지는 positive PR과 PR로 가려진 부분이 없어지는 negative PR이 있고,

이 과정은 Develop에서 구분됩니다.

파장이 짧은 파란빛을 제거한 yellow room에서 공정이 진행되고, spin coating을 통해 액체 PR을 고르게 코팅합니다.

- Etching

Etching은 필요 없는 부분을 없애주는 공정으로,

위의 Photolithography공정과 ethcing을 통틀어 Patterning과정이라고 합니다.

etching은 모든 방향으로 고르게 되는 Isotropic과 방향성을 가지고 진행되는 Anisotropic으로 구분됩니다.

Etching에서 사용되는 parameter를 보면,

우선 etch rate(E/R)는 얼마나 빠르게 etching이 진행되었는지를 나타내고, nm/s의 단위를 가집니다.

그리고 etch selectivity는 물질에 얼마나 선택적으로 etching하는지를 나타내고, etch rate의 비율과 같습니다.

예를들어 물질 A의 etch rate가 1nm/s, B의 etch rate가 10nm/s이면 etch selectivity는 0.1이 됩니다.

etching의 방법에도 두가지가 존재합니다.

액체 상태의 용액을 사용하는 wet etching은 SiO2 etching에 좋은 방법입니다.

그리고 plasma를 주로 사용하는 dry etching은 plsma인 'F'를 사용해 반응성이 매우 좋습니다.

- Thin film

Thin film은 말그대로 얇은 film을 증착하는 과정입니다. 종류는 크게 두가지 존재합니다.

① CVD (Chemical Vapor Deposition)

공정을 진행하는 방인 chamber에 가스형태의 물질을 주입하여 wafer(substrate)위에 film을 형성하는 방식입니다.

반응을 위해 넣어주는 가스를 precusor라 하고, 여기에 열 heat를 가해주게 됩니다.

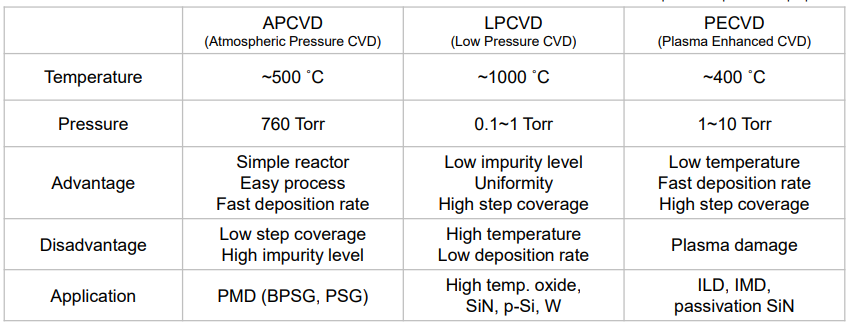

위 세 방식은 다른 환경에서 진행되는 CVD입니다.

deposition rate (thickness/time)은 시간 당 증착되는 두께를 말하고,

step coverage는 wafer 표면에 step이 있을 때, step의 옆면에도 고르게 증착되는지를 나타내는 parameter입니다.

압력이 높을 때는 wafer사이에 기체가 많이 들어갈 수 있고, 반대로 압력이 낮으면 기체가 덜 들어가있는 환경입니다.

각 상황에서 어떤 특징을 가지는지 확인하면서 보면 되겠습니다~

이러한 CVD를 진행하는 방식도 크게 두가지로 나뉩니다.

wafer 한 장씩 진행하는 single type은 균일하게 CVD가 이루어 지는 장점이 존재합니다.

반면 wafer 여러장을 동시에 진행하는 batch type는 시간 당 처리할 수 있는 wafer 장수를 나타내는 throughput이 높습니다.

이 batch tyope에서 wafer를 세워두고 하면 상대적으로 덜 균일하게 되어 눕혀놓고 하는 것이 더욱 효과적입니다.

CVD와 비슷하게 ALD, Atomic Layer Deposition도 존재합니다.

ALD는 말 그대로 원자를 한 층씩 천천히 얇게 증착하는, layer-by-layer로 순서대로 진행하는 방식입니다.

각 cycle이 존재하고 이를 control 하기 때문에, time을 control하는 CVD와의 차이점을 가집니다.

1. Precursor 공급

2. Purge

3. Reactant 공급

4. Purge

위 네 순서대로 진행한 뒤, 다시 처음부터 계속 cycle을 진행합니다.

Purge는 1과 3 과정에서 표면에 달라붙지 못한 물질들을 Ar같은 물질을 넣어주면서 밖으로 빼내는 것을 말합니다.

ALD는 컨트롤 하기 쉽고, 골고루 증착이 가능하고 step coverage가 높고 온도가 낮은 장점을 가지지만,

반면 deposition rate가 낮아 throughput이 낮기 때문에 시간 단위로 보면 긴 과정을 진행한다는 단점도 존재합니다.

② PVD (Physical Vapor Deposition)

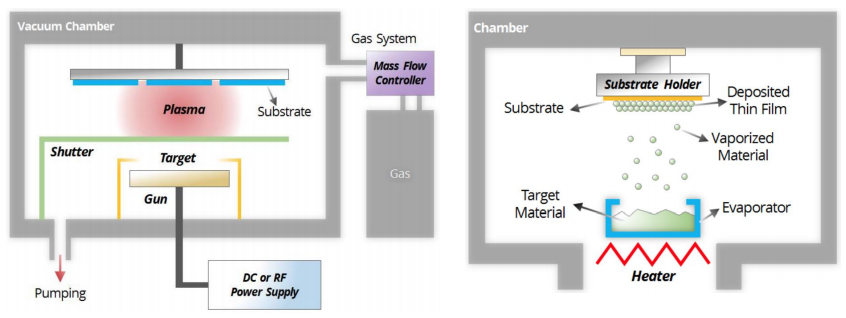

PVD는 물리적인 방법으로, vapor를 밑으로 향하게 한 뒤, 아래에서 진행하는 방식을 말합니다.

주로 plasma로 ion의 충돌을 이용하는 sputtering 방식과,

thermal을 가하거나 e-beam을 통해 heating시켜 튀어나오게 하는 evaporation방식이 존재합니다.

- Diffusion

Diffusion은 고농도에서 저농도로 이동하는 현상을 말하고, 이 과정으로 결과적으로는 전체적으로 같은 농도가 됩니다.

이러한 diffusion은 doping물질인 dopant로 인해 일어나게 됩니다.

공정에서 diffusion은 Ion Implantation에서 볼 수 있습니다.

E-field로 가속된 이온을 사선으로 wafer에 충돌시켜 주입하는 공정을 말합니다.

많은 carrier들이 주입되는 거리를 projected range, Rp로 깊이를 control하고,

에너지가 높을수록, 원자번호가 작을수록(가벼울 수록) 더 깊게 주입됩니다.

이 과정은 dopan와 substrate의 선택지가 많고 낮은 온도에서 가능하다는 장점이 있지만,

damage가 발생하면서 lattice 구조가 변경될 수도 있다는 단점을 가집니다.

이렇게 damage를 입게 된 Si는 amorphization 되는데,

x<Rp에서는 vacancy rich 원자가 비어있고, x>Rp에서는 interstitial rich 밀려난 원자가 어중간하게 껴있게 됩니다.

이를 메꿔주기 위해서, heat를 가해주면 diffusion이 계속 일어나 vacancy에 interstitial이 들어가게 만듭니다.

lattice damage를 수리하고, dopant를 Si가 있었던 곳에 넣어주기 위해서 위와 같이 열을 가해줍니다.

dopant가 빈자리에 들어갈 수 있는 상황은

1. vacancy mechanism : 빈 자리에 들어가면서, dopant 움직임과 vacancy움직임이 같아진 상황

2. interstitial mechanism : 원자번호가 작은(크기가 작은) 물질들이 사이 공간에서 움직이는 상황

두가지를 확인할 수 있습니다.

transistor의 scaling으로 인해 다양한 문제들이 발생하게되고, 이러한 문제를 막기 위해 junction의 증착을 얇게 한 Shallow junction을 사용합니다.

이 Shallow junction을 만드는 방법으로는,

① Rp 줄여 implant 자체를 얇게 합니다.

에너지를 작게하고 무거운 분자를 사용, buffer를 놓고 진행하거나 사선으로 implantation을 진행하면 됩니다.

② diffusion을 줄입니다.

dopant를 재분배 함으로써 공정 시간을 줄이고(RTP, RTA) 가하는 총 열의 양을 줄입니다.

- Metallization

IC 소자들을 효과적으로 연결하기 위해서 금속 metal을 사용합니다.

금속은 resistance가 낮고, 잘 붙어있으며, 안정된 상태를 유지하기 때문이죠.

이러한 metal을 증착하는 과정이 metallization이 됩니다.

효율적인 metallization은 chip사이즈를 줄이고, 속도를 높이고, 유연함을 보이게 됩니다.

위 사진처럼 transistor들을 metal로 연결할 수 있습니다.

metal과 poly의 interface를 contact라고 하고, metal과 metal이 이어진 부분을 via라고 합니다.

intermetal dielctrics는 metal 사이에 있는 유전체들을 말합니다.

meatl은 RC delay로 성능을 확인할 수 있습니다.

아래 표는 다양한 종류의 물질들의 resistivity와 녹는점을 나타낸 표입니다.

추가적으로, interconnect 물질들을 비교한 표는 다음과 같습니다.

metal과 semiconductor가 맞닿아 있는 부분은 전류가 잘 흘러야 됩니다.

그 상황을 만들기 위해 MS 구조에서 확인했던 Ohmic contact가 가장 좋은 상황이 될 것입니다.

하지만, Ohmic contact는 만들기 어렵기 때문에, Schottky contact 상황을 Ohmic처럼 작동하게 만들어야 합니다.

Schottky contact 상황에서 doping농도를 높이면 depletion width가 작아지게 됩니다.

이로 인해 tunneling distance가 감소해 tunneling이 증가하게 되고, 이는 Ohmic contact처럼 작동하게 만들어 줍니다.

contact resistance는 metal과 Si 사이의 interface에 만들어 지는 resistance입니다.

silicon과 metal이 합쳐진 Silicide물질을 사용하면 이 resistance값을 낮출 수 있습니다.

CMP는 Chemical mechanical polishing으로, pad 위에 wafer를 두고 화학적, 기계적으로 표면을 평평하게 만드는 공정 기술입니다.

chemicla solution과 prticle적인 기술이 모두 사용되었다는 점을 이름에서 부터 알 수 있습니다.

낮은 resistivity와 녹는점을 가진 Cu는 이 방식을 사용한 Domascene process로 patterning을 합니다.

미리 trench형태의 구조를 형성해 두고, Cu를 채운 다음 CMP공정을 통해 표면을 갈아줌으로써 metal을 형성합니다.

- EDS

EDS는 Electrical Die Sorting으로, 공정이 끝난 chip을 검사하는 과정입니다.

yield = pass chip / total chip 으로 수율을 나타내고,

EDS에서 수율이 낮으면 이전의 단계로 돌아가서 수율을 높이는 방향으로 수정하게 됩니다.

- Packaging

전기적으로 transistor를 연결해 주고 chip을 보호하게 만드는 과정을 말합니다.

PCB라는 frame을 씌우는 과정을 진행하는데,

metal의 끝을 wire로 연결하는 wire bonding은 size가 증가헤 scaling limit가 존재하고,

내부 통로를 wire로 연결하는 through silicon via(TSV)는 density가 높고 비용이 많이 발생합니다.

결과적으로 CMOS Fabrication은 다음과 같이 정리할 수 있겠습니다.

수업에서는 2, 3주차의 내용이어서 조금 길긴 하네요

다음은 resistance와 capacitance에 관하여 반도체 소자 물리적으로 다룬 내용을 정리해 보겠습니다!

글 읽어주셔서 감사합니당 :-)

'[학부 일기] 전자공학과 전공 > 반도체 소자 및 설계' 카테고리의 다른 글

| [반도체소자및설계] Device Physics - Memory Device (1) | 2022.05.26 |

|---|---|

| [반도체소자및설계] Device Physics - MOSFET Technology (0) | 2022.04.17 |

| [반도체소자및설계] Device Physics - scaling (2) | 2022.04.15 |

| [반도체소자및설계] Device Physics - MOSFET (1) | 2022.04.13 |

| [반도체소자및설계] Device Physics - Resistance & Capacitance (1) | 2022.04.11 |