안녕하세요!!

오늘은 '반도체 소자 및 설계' 에서 MOSFET 기술에 대한 내용들에 대한 내용들 입니다!

다양한 MOSFET의 구조와 사용되는 각 기술들에 대해 이야기 해보겠습니다!

MOSFET device design의 목표는

on current는 높이고, off current는 줄이고, V_th는 유지해야 하며, SCE를 억제해야 합니다.

또 gate controllability를 높이는, Cox를 높이는 방향으로 진행해야 합니다.

- DG(Double Gate) MOSFET

channel의 아래쪽에 off current가 흐르는 leakage region은 drain의 영향을 많이 받게 됩니다.

그래서 이러한 영역의 gate controllability를 높이기 위해 2개의 gate, top gate와 botton(back) gate을 달아줍니다.

drain에서 source 방향으로 흐르는 E-field를 두 gate로 조절함으로써 더 정확하게 control시킬 수 있습니다.

이 구조는 drain의 영향이 적어지면서 Short channel effect가 줄어들게 되지만,

기존 mosfet을 만드는 공정과 적합하지 않고, 복잡하기 때문에 compatible한 단점이 있습니다.

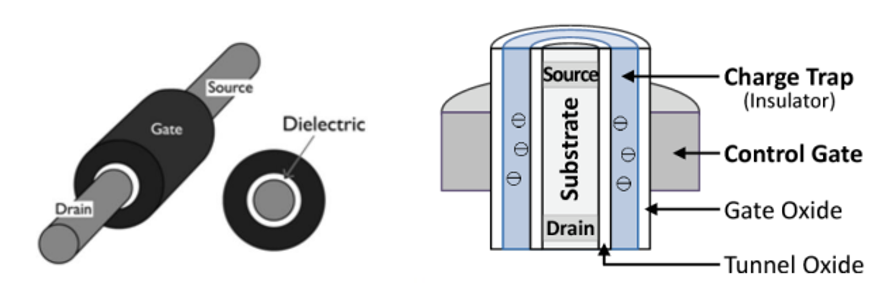

- GAA(Gate All Around) MOSFET

gate가 channel을 감싸고 있는 구조로, gate controllability 가 증가하게 됩니다.

control gate가 둘러싸여 있고, oxide와 Si body가 안에 들어있습니다.

Si 내부에 dielctric filter가 존재하는 경우도 있습니다.

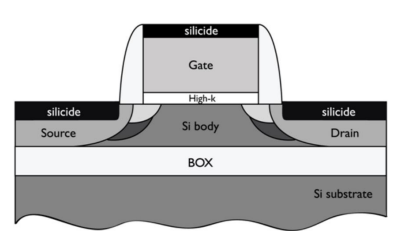

- SOI(Silicon-On Insulator) MOSFET

Si 내부에 절연체인 Buried oxide, BOX를 넣어준 mosfet 구조를 말합니다.

기존 mosfet에서 gate와 떨어진 channel 영역 아랫 부분에 off current가 흐르는

leakage path(path of I_off, conduction path) 를 BOX를 넣어줌으로써 leakage current을 줄여줄 수 있습니다.

이 구조의 특징은

① S와 D에 생긴 pn junction에 원치않은 cap이 생기게 되는데,

이 capacitance를 junction capacitance, parasitic capacitance라고 하고,

junction이 짧아지면서 이 capacitance를 이를 감소시킬 수 있습니다.

② 고립된 구조가 형성되기 때문에 latch-up이 없어집니다.

③ 기존 mosfet에서 BOX만 추가된 구조이기 때문에, 기존 Si processing과 호환 가능하다는 장점이 있습니다.

하지만 이러한 과정이 복잡하고, 비싸다는 단점 또한 존재합니다.

전류가 흐르면 Joule heating으로 인해 I^2R만큼의 열이 발생하게 됩니다.

기존 mosfet은 channel에 전류가 흘면서 열이 발생하지만, 아래 body쪽으로 빠져나갈 수 있게 됩니다.

그러나 BOX에 막혀 빠르게 열이 빠져나가지 못해 온도가 높아지게 되고, 발열문제가 발생하게 됩니다.

이러한 현상을 Self-heating effect라고 합니다.

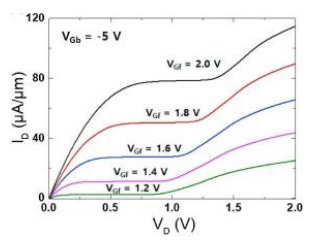

SOI MOSFET의 구조는 body의 두께에 따라 두가지 종류로 나눌 수 있습니다.

1. PDSOI (Partially depleted SOI) : W_dep,max < t_si

이때는 neutral body가 존재, 중성 영역이 남아있는 상태입니다.

기존의 MOSFET과 작동방법이 비슷한데, PDSOI에는 floating body effect가 존재합니다.

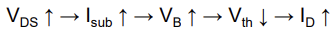

이 효과는 BOX에 의해 neutral 영역에 갇혀있게 된 h+가 쌓이면서 body voltage가 증가하게 되고,

threshold voltage가 감소하게 되는 현상을 말합니다.

이렇게 carrier가 증가하면서 I_d가 증가하는 kink effect가 발생하게 됩니다.

위 현상들을 정리하면 다음과 같이 나타낼 수 있습니다.

이 drain current는 saturation되다가 높은 V_D에서 갑자기 증가하는 모습을 보입니다.

2. FDSOI (Fully depleted SOI) : W_dep,max > t_si

이름에서 알 수 있듯이, 이 상황은 neutral body가 존재하지 않고 body역역이 모두 depletion된 상황이 됩니다.

FESOI에서는 PDSOI와는 다르게 floating body effect가 발생하지 않고, kink off도 발생하지 않습니다.

그리고 subthreshold swing이 ideal하게 되는데, ideal한 값인, 60mV/dec와 비슷한 값으로 감소하게 됩니다.

C_dep는 W_dep가 감소함에 따라 증가하게 됩니다. 그러면서 SS또한 감소하게 되기 때문에 SS가 감소한다고 말할 수 있겠습니다.

그리고 FDSOI에서는 Ultra-thin body를 사용합니다.

- Strain Silicon

Si를 SiGe에 epitaxy시키는 상황을 생각해보면, Si의 구조는 SiGe의 구조에 따라가게 됩니다.

이렇게 lattice 구조가 늘어나게 되는 것을 tensile strain이라 하고, 반대로 줄어들게 되는 상황을 compressive strain이라 합니다.

Tensile strain이 발생하면,

Si lattice constant가 증가하고, scattering이 감소하게 됩니다.

이로인해 속도가 증가하면서 mobility도 증가하게 되고, 최종적으로 on current가 증가할 수 있습니다.

따라서 channel 영역에 strained Si를 사용하게 되면, on current를 증가시킬 수 있게 됩니다.

위 그래프에서 -방향은 compressive, +방향은 tensile strain을 나타내게 됩니다.

tensile strain이 일어날수록 drain current가 증가하는 것을 확인할 수 있습니다.

- Fin FET

Fin FET 구조는 leakge path를 없애고 gate controllable을 높이기 위해 사용하는 구조를 말합니다.

좋은 성능을 가지고 있지만, 이 구조는 공정에서 발생하는 여러 어려움들이 존재합니다.

① Fin 모양을 일정하게 유지하기 어려움

② parasitic capacitance(fringe capacitance)가 증가하게 됨

③ S, D의 doping농도를 유지하고, 높이기 힘듬

그리고 모든 MOSFET에서 발생하는 LER(Line Edge Roughless) 또한 발생하게 됩니다.

소자의 표면이 울퉁불퉁하게 만들어져 W, L이 변하게 되고, 결국 소자 자체의 특성이 변하게 되는 것을 LER이라 합니다.

- EOT&CET

MOSFET의 총 두께를 나타내는 방식, POT(Physical oxide thickness)에는 두가지가 있습니다.

1. EOT

EOT는 Equivalent Oxide Thickness로, SiO2관점에서 봤을 때, high-k 물체의 두께를 말합니다.

위 식을 통해 EOT를 구할 수 있고, 이를 이용해 실질적인 두께가 아닌 SiO2와 비교해서 느껴지는 oxide의 두께 차이를 확인할 수 있습니다.

예를들어, 20nm의 Al2O3(k=8)과 HfO(k=16)이 존재할 때, 각각의 EOT는 10nm와 5nm가 됩니다.

실제 두께는 같지만, SiO2관점에서는 Al2O3가 HfO보다 2배 큰 값을 가지고 있는 것을 알 수 있습니다.

2. CET

CET는 Capacitance equivalent thickness로, MOSCAP을 형성했을 때, 그 사이 형성되는 전체 영역을 고려한 두께가 됩니다.

이 값은 computer로 측정을 해서 확인할 수 있는 값이 됩니다.

- High-k dielectric

앞 게시글에서 SCE는 lateral scaling이기 때문에, vertical로 scaling해주는 방향으로 이를 줄일 수 있다고 언급했습니다.

이 방식이 vertical한 방향으로 scaling하는 방법이고, t_ox를 줄임으로써 C_ox를 증가시키는 방향으로 진행하게 됩니다.

보통 oxide를 줄이는 것은 POT를 줄이는 방식으로 진행합니다.

하지만 무작정 t_ox를 감소시키면 direct tunnling이 발생할 만큼 band banding이 커지게 되면서 leakage current가 발생하게 됩니다. 즉, 한계가 존재한다는 것이죠.

그래서 사용한느 것이 high-k 물질을 사용해 EOT를 줄이는 것 입니다.

high-k물질은 ALD로 공정하여 증착시킬 수 있는데, 이 또한 문제점이 존재합니다.

① k가 증가할 수록 energy band gap, band offset이 감소하게 됩니다.

band offset은 junction에서 conduction band의 edge차이를 말하는데,

이 parameter가 작을수록 carrier들이 쉽게 넘어다닐 수 있게 되기 때문에 이러한 상황을 막는게 중요하겠습니다.

② 또, trap이 증가하게 되면서 SiO2보다 불안정한 특성을 가지게 되는 문제점도 있습니다.

- Metal gate

MOSFET에서 주로 사용하는 gate는 Pilysilicon gate입니다. highly-doped 물질이죠.

쉽고 간단한 공정을 진행할 수 있고, gate depletion effect를 줄여줄 수 있지만,

추가적으로 C가 생성되기 때문에, C_ox가 감소하게 되는 치명적인 단점이 존재합니다.

그래서 사용하는 물질이 metal gate입니다.

metal gate를 사용하면 gate depletion effect가 발생하지 않기 때문에 C_ox를 증가시킬 수 있습니다.

resistance도 감소해 drain current도 증가할 수 있고,

gate WF(work fuction)을 이용해 Vth를 조절할 수 있습니다.

이 metal gate는 high-k와 주로 사용하기 때문에, 이러한 구조를 HKMG라 합니다.

오늘 글은 여기까지입니다!

이번 게시물 까지가 중간고사 범위, 7주차 강의였습니다 ..!!

이젠 중간고사 끝나고 기말고사 공부를 할 때 다시 돌아오도록 해야겠어요 ㅎ.ㅎ

다들 화이팅 !!!!!

글 읽어주셔서 감사합니다 ㅎㅎ

'[학부 일기] 전자공학과 전공 > 반도체 소자 및 설계' 카테고리의 다른 글

| [반도체 소자 및 설계] Device Physics - Display TFT (3) | 2022.05.29 |

|---|---|

| [반도체소자및설계] Device Physics - Memory Device (1) | 2022.05.26 |

| [반도체소자및설계] Device Physics - scaling (2) | 2022.04.15 |

| [반도체소자및설계] Device Physics - MOSFET (1) | 2022.04.13 |

| [반도체소자및설계] Device Physics - Resistance & Capacitance (1) | 2022.04.11 |