안녕하세요!!

오늘 반소 게시글은 layout에 관한 내용입니다.

제가 가장 재밌게 배웠던 부분인데, layout에 대해 많은 그림들과 같이 알아보도록 하겠습니다!!

- Photo mask & Layout

photo mask는 photolithography lecture를 말하고, 이를 pattern화 한 것이 layout이 됩니다.

즉, layout은 회로도를 원하는 모양으로 만들기 위한 2차원의 그림을 말하는 것입니다.

이 layout은 design rule에 따라 제작됩니다.

layout은 transistor의 사이즈, 배선의 간격/깊이 등을 결정하기 위해 minimum dimension을 정해둡니다.

minimun dimension은 minimum rule을 바탕으로한 최소한의 면적 구조 layout으로, 집적도가 높습니다.

test를 통해 구한 최소값을 사용하게 되고, 회로도가 같더라도 layout은 달라질 수 있습니다.

같은 회로도에서 junction을 이어주거나 다양한 방법으로 면적을 줄일 수 있게 되는것이죠.

다음 그림과 같이 junction이 이어질 수 있는 것입니다.

pMOS의 h+과 nMOS의 e-의 mobility 차이는 약 2배정도 차이가 나는데,

이로 인해 dimension의 차이도 nMOS보다 pMOS가 2배 큽니다.

이에 대한 자세한 내용은 다음 게시글에서 적어보겠습니다!

- Inverter layout 제작과정

우선 inverter는 input의 반대가 output으로 출력되는 소자입니다.

0이 입력으로 들어가면 1이 출력되고, 1이 들어가면 0이 출력되는 소자입니다.

이 inverter의 layout을 제작해 봅시다.

우선 inverter의 최종 layout은 다음과 같습니다.

nMOS와 pMOS 두개가 이어져, 각 MOSFET의 입력에 따라 output이 결정됩니다.

input은 A로, output은 Y로 나타나져 있습니다.

위 layout은 다음과 같이 6장의 mask로 구성되게 됩니다.

well은 pn junction을 형성하기 위해 사용하게 됩니다. 이를 well tap이라고 합니다.

substrate tap은 diode가 forward되어 원치 않을 때 on이 되지 않게 막아주는 역할을 합니다.

그리고 layout의 빈 부분에는 LOCOS, STI와 같은 물질을 이용해 가까운 transistor와의 간섭을 최소화 시켜줍니다.

isolation을 시켜 전류가 흐르지 못하게 하는 것이죠.

이제 이 과정을 차례로 살펴봅시다.

※ inverter layout 제작과정

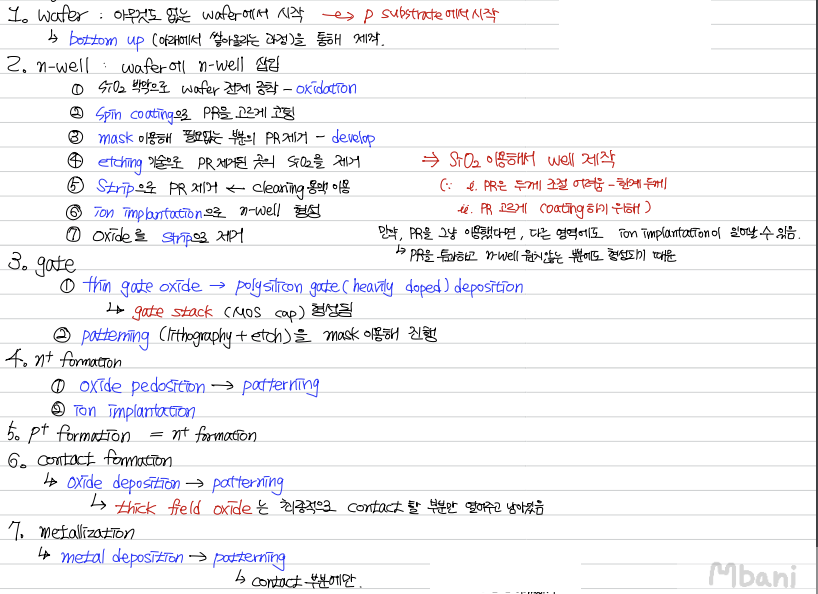

1. wafer

아무것도 없는 wafer에서 시작, p substrate에서 시작

layout은 bottom up, 아래에서 부터 쌓아 올리는 과정으로 제작

2. n-well

① SiO2 박막을 wafer 전체에 oxidation

② spin coating을 통해 PR 고르게 코팅

③ mask를 이용해 필요없는 부분의 PR을 제거 (develop)

④ etching을 통해 PR이 없는 부분의 SiO2 제거

⑤ strip 기술로 PR 제거 (cleaning 용액)

⑥ ion implantation으로 n-well 형성

⑦ oxide를 strip으로 제거

이 공정 과정을 보면, SiO2를 이용해 well을 제작하는 것을 알 수 있습니다.

이는 PR 두께를 조절하는데 한계가 있고, PR을 고르게 coating하기 위해 SiO2를 사용하는 것 입니다.

만약 PR을 그냥 사용했다면, 다른 영역에도 PR이 투과, ion implantation이 발생해 원치 않는 구조가 만들어 질 수도 있을겁니다.

3. gate

① thin gate oxide를 위해 heavily doped polysilicon gate를 deposition -> gate stack(MOScap) 형성

② patterning 진행

4. n+ formation

① oxide deposition -> patterning

② ion implantation

5. p+ formation

= n+ formation

6. contact formation

oxide depisition -> patterning -> thin field oxide는 contact 부분을 제외하고 남아있게 됨

7. metallization

metal deposition -> patterning -> contact 부분에만 진행

위 과정을 차례로 그린 것이 다음과 같습니다!

( + 필기 자료도 아래에 추가했습니다!)

- Layout vs Real pattern

이렇게 만들어낸 layout은 실제 제작되는 pattern과 다른점이 생기게 됩니다.

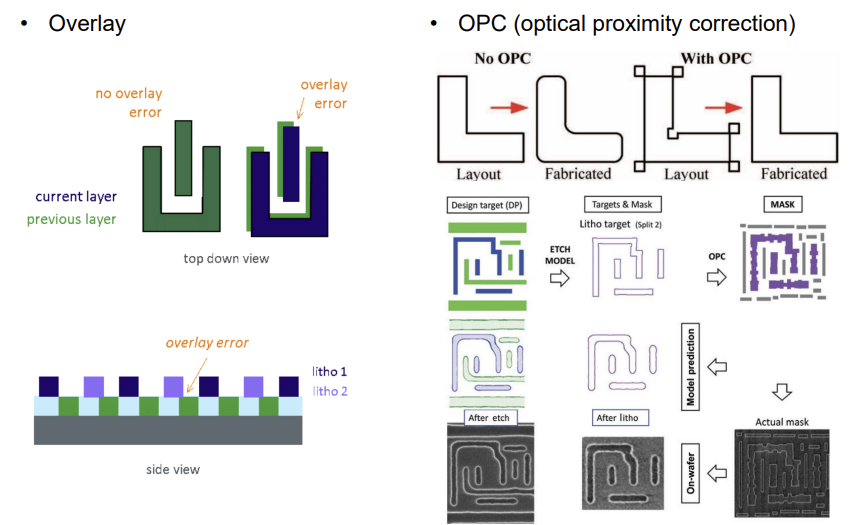

1. Lithography

overlay로 인해 여러 층들 간 정렬이 맞지 않아지면서 동작이 달라질 수 있습니다.

또, 뾰족한 부분의 모양이 바뀌는 현상이 발생하면 이를 막기 위해 OPC(Optical Proximity Correction)을 사용합니다.

2. Etching

etching profile은 non-ideal해서 TCD(top critical dimension)과 BCD(bottom critical dimension)이 달라질 수 있습니다.

이때의 CD는 etching한 뒤 생기는 사이즈 변화를 말하며, 주로 TCD>BCD가 심합니다.

이러한 현상은 bowing 현상을 원인으로 하고 이온들의 충돌로 경로가 변경됩니다.

특히 윗 부분은 충돌이 많아 옆면을 때리며 non-ideal한 경로가 형성되고, 아래는 상대적으로 충돌이 적어 고르게 내려오면서 TCD가 BCD보다 심하게 일어나게 됩니다.

이러한 현상을 예측하고 간격의 사이즈를 미리 정해야만 막을 수 있습니다.

3. Diffusion

transistor가 만들어 진 이후로 열이 가해지면 thermal diffusion으로 layout과 real pattern이 달라질 수 있습니다.

이는 Lg(layout) ≠ Lg(real)을 고려하여 layout을 제작해야 합니다.

높은 pn junction의 농도, 큰 heat budget, 큰 impurity, 복잡한 구조일수록 diffusion이 더 많이 일어나기 때문에 이를 잘 고려해야 합니다.

결론적으로는길이가 짧아지면 roll off가 심화되고 off current가 증가하기 때문에,

real pattern이 layout과 같아야지만 원하는 작동을 하게 됩니다.

오늘 게시글은 여기까지 입니다!

Layout 제작 과정을 그려보면서 하면 더욱 이해하기 쉽더라고요..!

다음 게시글은 ESD&Latch-Up&Logic gate에 대해 정리해 보겠습니다.

감사합니다~!

'[학부 일기] 전자공학과 전공 > 반도체 소자 및 설계' 카테고리의 다른 글

| [반도체 소자 및 설계] Circuit Engineering - Antenna Effect, Power, Trade offs, Reliability (0) | 2022.08.31 |

|---|---|

| [반도체 소자 및 설계] Circuit Engineering - ESD&Latch-Up&Logic gates (0) | 2022.08.29 |

| [반도체 소자 및 설계] Device Physics - Failure Analysis (0) | 2022.08.28 |

| [반도체 소자 및 설계] Device Physics - Display TFT (3) | 2022.05.29 |

| [반도체소자및설계] Device Physics - Memory Device (1) | 2022.05.26 |