안녕하세요!

이번 글은 '반도체 소자 및 설계' 에서의 ESD, Latch-Up, Logic gate에 대해 알아보려 합니다.

각각 다른 내용이기 때문에 하나씩 살펴보도록 하겠습니다.

< ESD >

ESD는 Electro Static Discharge의 약자로,

정전기와 같이 매우 높은 전압이 순간적으로 소자에 들어오게 되면서 gate oxide, metal interconnection에 손상을 입는 것을 말합니다.

이를 해결하기 위해 ESD protection circuit을 사용하여 CMOS device에서 ESD를 막아주는 역할을 수항하게 됩니다.

ESD protection의 종류에는 current limiting resistor, diode clamps 등이 있습니다.

위 사진은 diode clamps 입니다.

input에 큰 전압이 들어올 때 device를 보호하기 위한 diode가 되겠습니다.

평소 상태에서는 D1, D2가 reverse bias상태가 됩니다.

만약, Vin>>0 일 때, D1은 forward bias가 걸리면서 전류는 supply rail로 빠져나가게 됩니다.

반면 Vin<<0 일 때, D2가 forward bias로 인해 on되고 전류는 ground로 빠져나가게 됩니다.

이러한 과정을 통해 device를 큰 전압으로 부터 보호해 줍니다.

< Latch-Up >

Latch-Up은 CMOS에서 n-channel과 p-channel device가 가까이 붙어 원치 않은 루트가 발생하는 것을 말합니다.

CMOS에 pnpn structure가 형성되게 되는 것입니다.

pnp의 전류가 npn의 base로 흘러 들어가 큰 전류가 발생하는 현상으로,

구조를 파괴할 정도의 high current, low-voltage condition을 발생시킵니다.

보통 CMOS는 cut-off 상태인데, 특정 조건에서 avalanche breakdown이 발생하게 되면 saturation 되면서 전류가 흐르기 시작합니다.

그러면 positive feedback을 따라 전류가 계속 증가하면서 damage를 입히는 premanent damage가 발생하게 되는 것이죠.

이러한 전류는 다음과 같이 표현할 수 있습니다.

이러한 Latch-Up 현상을 줄이는 방법은 다음 두 가지가 존재합니다.

① lowering β

β는 Base에서 Collector로 얼마나 전류가 증폭되는지를 나타내는 parameter입니다.

이를 줄이기 위해서는.

recombination rate를 impurity doping으로 증가시켜 SRH(Shockley Read Hall) recombination을 발생시킬 수 있습니다.

SRH recombination은 Si bandgap 내부에 생긴 state로 인해 recombination되는 것으로,

impurity가 증가하면 bandgap 내부의 state가 증가하기 때문에 발생할 수 있게 됩니다.

또, 두께 thickness를 증가시켜 recombination을 늘려 β를 감소시킬 수 있으나, scaling과 반대되는 상황이 됩니다.

② isolation

각 transistor 사이를 고립시키면 자연스럽게 latcup-up도 감소합니다.

이를 위해 STI, FDSOI 등을 이용하거나 전통적 latch-up 방법인 Guard ring을 만드는 방법도 있습니다.

guard ring은 parasitic BJT를 방지하기 위해

PMOS(n-well)에는 n+ ring (V_DD)을 만들어 p+에 생기는 minority carrier(e-)를 n+ ring을 통해 바로 빠져나가게 하고,

NMOS(p-well)에는 p+ ring (GND) 을 만들어 n+에서 생기는 h+를 p+ ring을 통해 바로 빠져나가게 하는 방식입니다.

guard ring은 자연스럽게 β도 감소시킬 수 있습니다.

< Logic gates >

- CMOS logic circuit

CMOS logic circuit은 inverter가 가장 간단한 형태를 가집니다.

우선, NMOS는 pull-down transistor라고 하며 PDN(pull down network)라고 하고,

PMOS는 pull-up transistor라고 해서 PUN(pull up network)라고 합니다.

PDN이 병렬이면 PUN은 직렬, PDN이 직렬이면 PUN은 병렬인 형태를 가집니다.

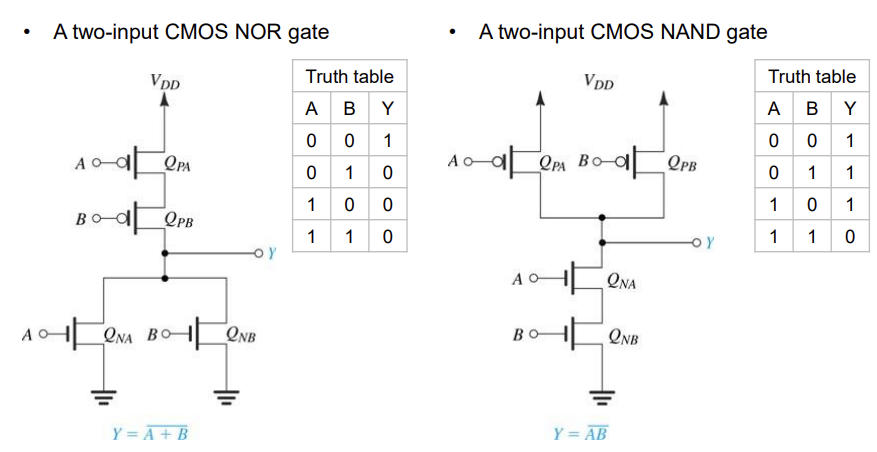

다음과 같은 예시들을 통해 이를 확인할 수 있습니다.

이와 같은 CMOS logic gate의 장점은 static current가 없고, stand by power dissipation이 적기 때문에 low power를 보인다는 것 입니다.

추가 예제로 다음 회로를 풀어보면 이해가 쉬울겁니다..!

그러면, NMOS와 PMOS가 왜 각각 PDN과 PUN으로 정해졌는지도 알아봅시다.

기존 상황에서는 Vgs>Vth가 되면 Vs=0이기 때문에 Vgs=Vg=Vin이 됩니다.

즉, Vth보다 큰 전압에서 NMOS가 켜지고 이로 인한 control을 진행하게 됩니다.

반대의 상황에서(NMOS가 PUN, PMOS가 PDN)는 Vgs=Vin-Vout>Vth가 되는 범위에서 동작이 가능해집니다.

Vout의 node는 Vdd-Vth 까지만 on되기 때문에 동작할 수 있는 범위가 기존보다 작기 때문에

NMOS는 PDN, PMOS는 PUN으로 사용하게 되는 것 입니다.

- transistor sizing

transistor의 size에 대한 이야기는 이전 게시글에도 잠깐 언급을 했었습니다!

e-과 h+의 mobility의 차이는 대략 μ_n = 2μ_p정도가 됩니다.

이러한 mobility차이를 극복하기 위해서는 Wp=2Wn이 되어야 성립하게 됩니다.

그리고 transistor의 size는 worst case matching을 사용합니다.

PUN과 PDN에 가장 전류가 적게 흐르는 상태를 가정하는데, 이는 직렬에서 모두 on, 병렬에서는 하나만 on되는 상황을 가정해서 구할 수 있습니다.

추가로, transistor는 cap처럼 직렬 병렬 특성이 합쳐지는 것 처럼 생각하면 쉽게 생각할 수 있습니다..!

또, AND와 OR gate는 NAND+inverter, NOR+inverter로 구성하여 제작합니다.

- layout of logic gate

복잡한 회로일 수록 layout의 경우의 수는 증가하기 때문에 디자인은 유지하면서 면적은 줄여야 합니다.

그리고 Metal-Semiconductor interface 사이 depletion 영역에 cap이 생기면 RC delay가 증가하기 때문에,

junction cap을 최소한으로 해야합니다.

오늘 게시글은 여기까지 입니다!

이제 다음 게시글이 '반도체 소자 및 설계' 탭의 마지막 글이 되겠네요.

다음 게시글까지 열심히 작성해보도록 하겠습니다!~!

'[학부 일기] 전자공학과 전공 > 반도체 소자 및 설계' 카테고리의 다른 글

| [반도체 소자 및 설계] Circuit Engineering - Antenna Effect, Power, Trade offs, Reliability (0) | 2022.08.31 |

|---|---|

| [반도체 소자 및 설계] Circuit Engineering - Layout (0) | 2022.08.29 |

| [반도체 소자 및 설계] Device Physics - Failure Analysis (0) | 2022.08.28 |

| [반도체 소자 및 설계] Device Physics - Display TFT (3) | 2022.05.29 |

| [반도체소자및설계] Device Physics - Memory Device (1) | 2022.05.26 |