안녕하세요!

오늘은 '반도체 소자 및 설계' 마지막 글입니다.

Antenna Effect, Power, Trade offs, Reliability에 대한 내용들을 하나씩 간단히 알아보도록 하겠습니다!

< Antenna Effect >

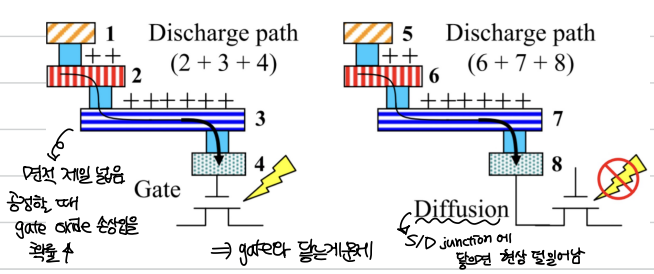

다양한 층 위에 metal 배선을 연결하면, metal이 드러나 있는 상황에서 plasma 공정을 진행하게 됩니다.

이온화된 plasma가 metal 위에 축적될 수 있게 되는 상황에서 plasma 이온들이 배선을 타고 gate까지 내려가게 되면서 의도치 않은 bias가 형성될 수 있게 됩니다.

이로 인해 gate oxide가 견딜 수 없이 큰 전압이 걸리게 되면 공정 도중 breakdown이 일어나게 되는데,

이러한 현상을 antenna effect라고 합니다. antenna 처럼 전하를 gate oxide로 이동시키기 때문에 이런 이름이 붙었습니다.

이 현상은 circuit layout rule에서 고려해야 하는 문제이기 때문에 antenna rule을 따라야 합니다.

antenna ratio = (plasma-exposed area)/(gate oxide area)의 비를 이용합니다.

transistor의 gate 이외의 S/D junction에 닿는 것은 문제가 덜 발생하는 것을 이용해 다음과 같이 antenna ratio를 감소시킬 수 있습니다.

① Jumper insetion : gate에 큰 영향을 주는 metal 영역의 경로를 변경해 면적을 줄이는 방법

② Layer assignment : layout design을 변경해 넓은 면적을 맨 위로 보내는 방법

③ Protection diode : 가장 면적이 큰 metal에 diode를 달아 plasma(빛) 받으면 reverse bias에서도 on되는 성질을 이용해 gate를 보호

< Delay & Power >

- Delay

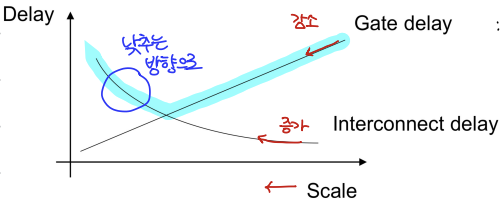

mosfet을 기준으로, Lch을 줄이면 on current가 증가하고 RC delay에 관여하는 capacitance가 감소하게 됩니다. 하지만 interconnection delay는 배선 단면적이 줄어들수록 R이 증가, 배선 간격이 줄어들수록 C가 증가하기 때문에 RC delay는 증가하게 됩니다.

gate 와 interconnection의 delay가 만나는 이전 상황의 delay를 낮추는 방향으로 설계를 진행해야 delay가 감소합니다.

RC delay를 줄이는 방법은 다음과 같습니다.

1) 저항 R 줄이기

- 저항이 낮은 물질을 사용

- 폭이 좁고 깊은 배선을 사용

이러한 과정은 공정이 어렵습니다.

2) 커패시턴스 C 줄이기

- 면적(A)을 줄이고 깊게(d 증가) 만들기

- 배선 사이 dielectric을 low-k 물질로 사용.

- 물성은 그대로, porous 박막을 사용

- Power

하나의 C에 charge를 진행할 때, power는 다음과 같이 구할 수 있습니다.

그러면 charge와 discharge를 진행하면 power는 위의 두배가 됩니다.

그리고 Dynamic(동작) power는 다음과 같습니다.

delay를 줄이면 high frequency의 고속 동작이 가능하기에 더 큰 dynamic power가 필요해 집니다.

따라서, power-delay product는 상수가 됩니다.

CMOS에서 dynamic power와 static power는 다음과 같이 나타낼 수 있습니다.

이러한 power consumption을 줄이는 방법은 다음과 같습니다.

ⅰ V_DD를 줄이기 -> 두 배로 감소 (dynamic, static 둘 다 감소)

ⅱ C를 줄이기

ⅲ switching activity를 줄이기 -> 동작 횟수를 최소화로 design

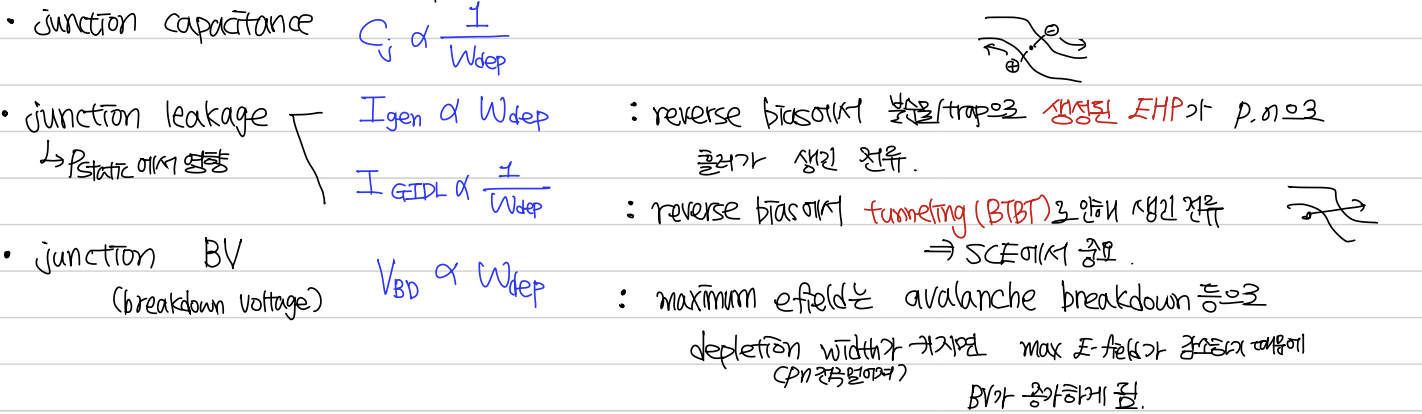

ⅳ static current(Ioff) 줄이기 -> generation currnet, GIDL 줄기고 Vth 변하지 않게

< Trade-off >

junction depletion width에 따른 trade off는 다음과 같이 존재합니다.

< Reliability >

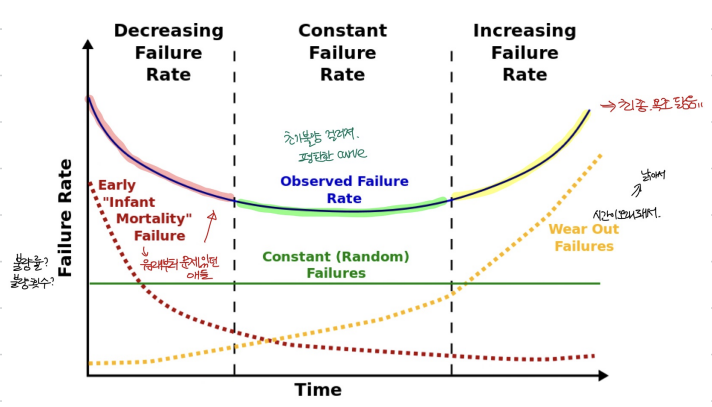

- bathtub curve

time-gailure rate 그래프는 욕조를 닮아 bathtub라고 불립니다.

- Reliability of transistor

transistor의 reliability는 다음 두가지로 크게 나눌 수 있습니다.

1. TDDB(Time Dependent Dielectir Breakdown)

gate oxide(dielectric film)에 stress를 줘 얼마나 동작을 하는지 life time을 평가하는 statistically(통계적) 방법입니다.

Q_BD( charge to breakdown)은 breakdown까지 얼마나 많음 charge가 oxide를 지나는지 나타냅니다.

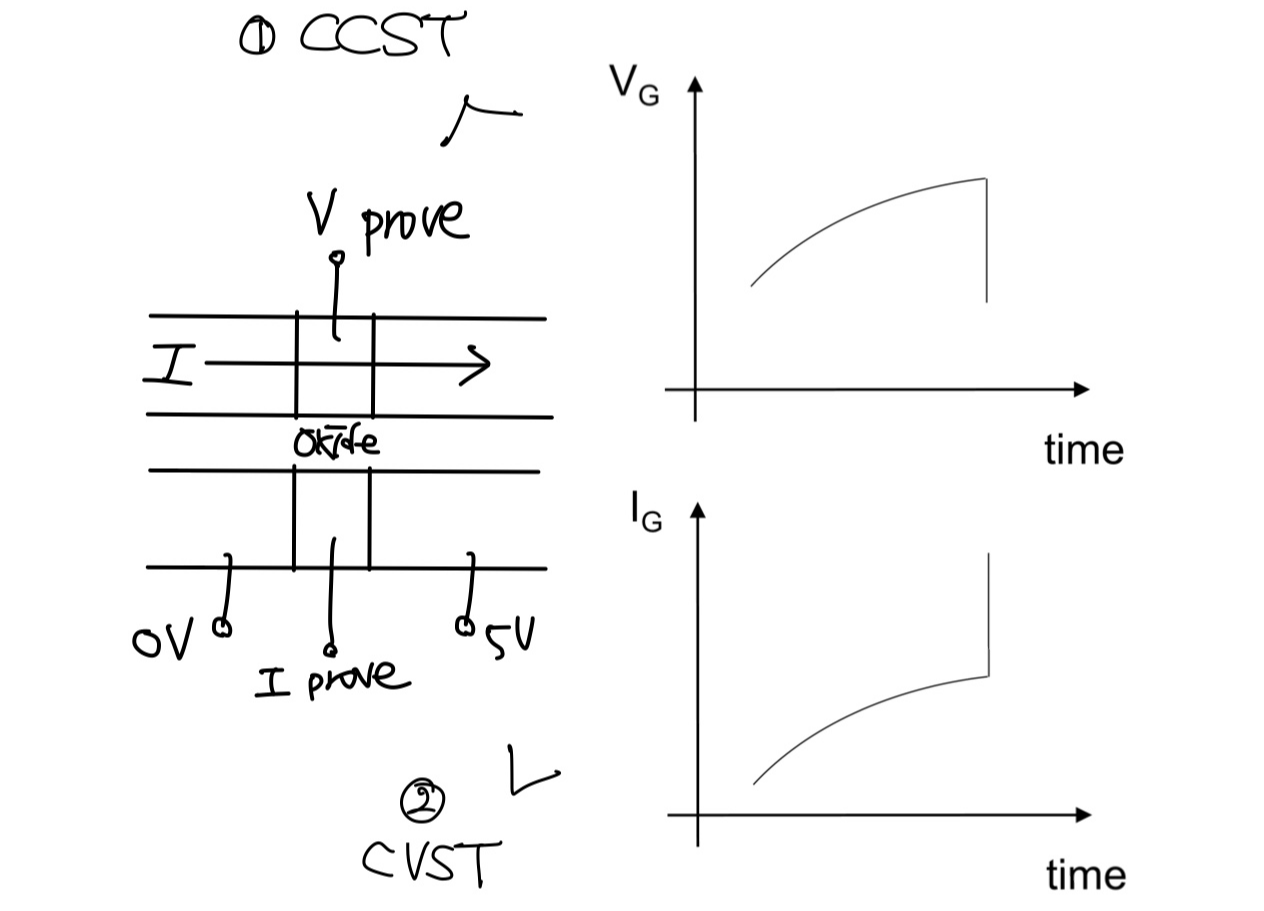

TDDB의 방법은 I를 일정하게 인가해 V_G를 측정하는 CCST(constant current stress test)와

V를 일정하게 인가해 I_G를 측정하는 CVST(constant voltage stress test)가 있습니다.

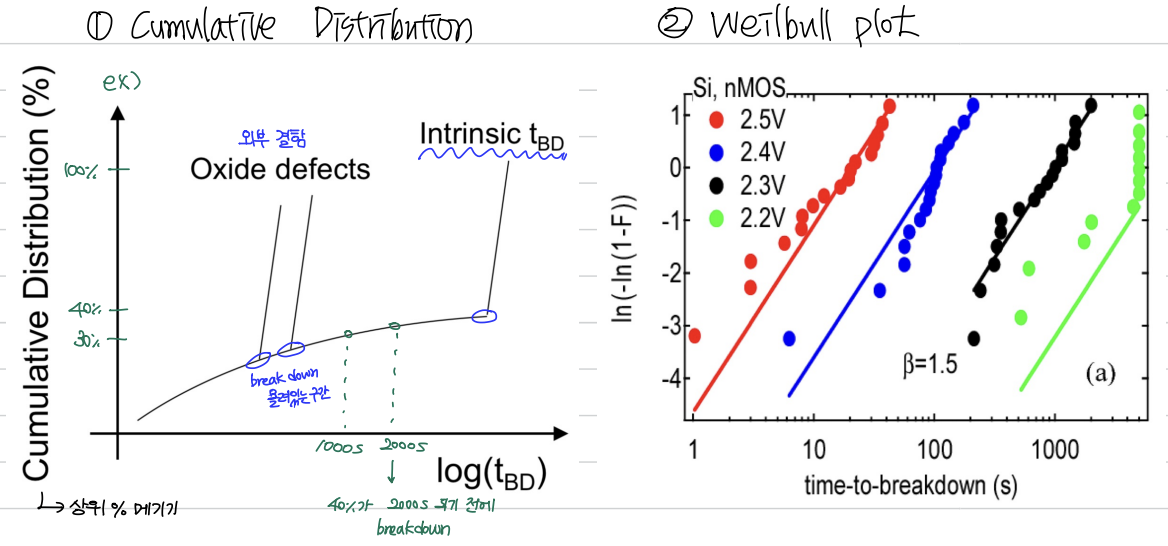

그리고 이를 표현하는 방법은 아래 두가지로, Cumulative distribution과 weilbull plot이 있습니다.

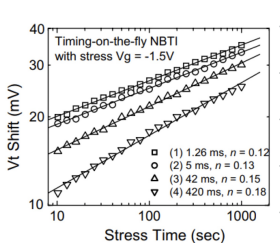

2. NBTI

NBTI(negative bias temperature instability)는 PMOS에,

PBTI(positive bias temperature instability)는 NMOS에 사용하는 방법으로

실제 사용하는 값보다 더 큰 bias와 온도를 인가하여 시간마다 transfer curve를 측정하는 방법입니다.

측정을 진행하면 Vth가 감소하고 Ion 감소, mobility 감소, SS 증가의 현상이 보입니다.

이 상황의 원인은 N_it(interface trap)과 N_ot(oxide fixed charge)로 인해 발생하는데,

oxide 쪽에 hole이 몰리면서 Si-H와 Si-O의 결합이 개지면서 trap이 생성, 이에 hole이 갇힘 등의 문제가 발생하게 됩니다.

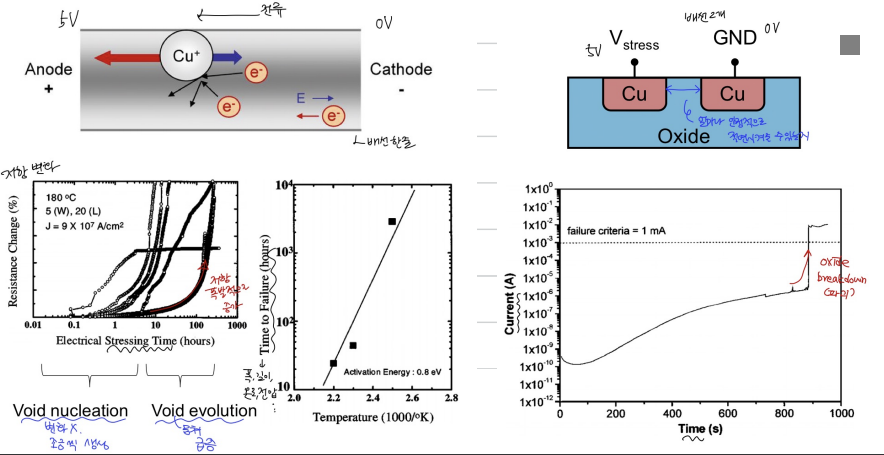

- Reliability of interconnect

interconnection의 reliability는 EM(Electromigrate)과 BTS(bias temperature stress)가 있습니다.

여기까지 입니다!

3학년 1학기 동안 진행한 수업이었고, 14주차 까지의 내용을 담아보았습니다.

이제 2학기에 진행하는 '반도체 공정 및 응용'으로 다시 공부를 시작해 보겠습니다!

감사합니다 ㅎㅎ

'[학부 일기] 전자공학과 전공 > 반도체 소자 및 설계' 카테고리의 다른 글

| [반도체 소자 및 설계] Circuit Engineering - ESD&Latch-Up&Logic gates (0) | 2022.08.29 |

|---|---|

| [반도체 소자 및 설계] Circuit Engineering - Layout (0) | 2022.08.29 |

| [반도체 소자 및 설계] Device Physics - Failure Analysis (0) | 2022.08.28 |

| [반도체 소자 및 설계] Device Physics - Display TFT (3) | 2022.05.29 |

| [반도체소자및설계] Device Physics - Memory Device (0) | 2022.05.26 |