안녕하세요!

3학년 2학기 종강 후, '반도체 공정 및 응용' 수업에대한 내용 정리를 해보려 합니다.

오늘 글은 반도체 공정 과정에 대한 전반적인 내용을 간단히 다루고 이후 글에서 각각 과정에 대해 자세히 다뤄보겠습니다!

'반도체 공정 및 응용' 과목의 전체 내용을 축약해둔 강의였다보니, 매우 짧고 간단하게 정리했습니다..!!

< Overall Device Fabrication Technology >

1. Silicon Wafer

모래 형태의 규소 Si는 sand 형태로 존재하고 있습니다.

여기서 Si만을 추출하기 위해 고온으로 가열하면 Metallic grade Si(MGS)를 만들어 낼 수 있는데, 이는 전기적으로 사용할 수 없기 때문에 Electronic grade Si(EGS) 형태로 제작하여 사용합니다.

이렇게 형성한 EGS를 가열 시켜 Seed crystal을 사용해 Ingot으로 형성한 뒤 자르게 되면 우리가 아는 Si Wafer를 만들 수 있습니다.

Seed Crystal은 만드려는 Si wafer의 plane number를 지정하는 역할을 합니다.

plane에 따라 Si의 원자 갯수가 달라지고 전기적 동작이 달라지기 때문에 지정할 때 중요한 요소가 됩니다.

그리고 가열 된 EGS에 추가적인 원소를 같이 녹이면, n-type/p-type과 같은 type을 지정할 수 있습니다.

2. Oxidation of Silicon

Oxidation은 산화를 말합니다. 이 과정은 다음과 같은 역할을 하는 산화막을 제작하는 역할을 합니다.

1) Masking Effect : 공정에서 들어오는 물질을 막아줌. patterning할 때 사용 됨.

2) Insulation : MOSFET의 gate와 channel 사이 전하 이동을 막기 위한, 즉 MOS contact을 막아줌. => 소자 내무 절연체

3) Dielectric layer : 소자 사이를 capacitance 형태로 막아주는 oxide

4) Passivation layer : electrode와 interconnection line 사이 막아주는 절연체. 미세 패턴을 형성할 때 short 방지.

Oxidation은 두 가지 종류로 나누고 각각의 장단점은 다음과 같습니다.

- Dry oxidation

Si + O2 -> SiO2 의 과정을 이용하여,

thin film과 high quality를 보이지만 반응 속도가 느림

- Wet oxidation

Si + 2H2O -> SiO2 + 2H2 의 과정으로,

빠른 반응 속도, thick film을 형성하지만 low quality를 보임

3. Photolithography

Photolithography는 빛을 이용해 패턴을 그려내는 과정을 말합니다.

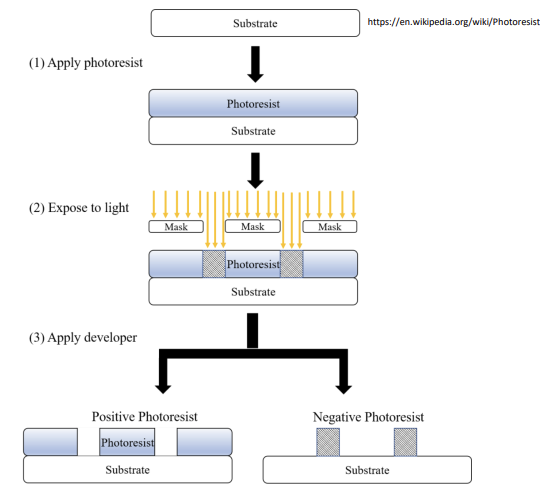

UV에 민감한 Photoresist(PR)을 사용하고 다음과 같은 과정을 따릅니다.

ⅰ PR coating - spin coating을 사용해 원심력으로 PR을 골고루 도포

ⅱ UV light exposure - photo mask를 통해 원하는 부분에 UV 빛을 비춰줌

ⅲ Development - 원하는 패턴을 형성하기 위해 없애는 부분의 성질을 변화시킴

- positive PR : 빛을 받은 부분을 날라가기 쉬운 형태로 변환

- negative PR : 빛을 받지 않은 부분을 날라가기 쉬운 형태로 변환

ⅳ Etching & PR strip - 없애는 부분을 제거 & 남아있는 PR을 제거

이때, 원하는 patern을 그리기 위해 mask를 사용하는데,

mask와 wafer는 공정의 연속성을 위해 항상 같은 자리에 위치시켜야 합니다.

이를 위해 Mask Align을 시키고, Mask Aligner를 이용해 mask의 Align key 표식을 사용해 둘의 위치를 맞춰줍니다.

4. Etching

Etching은 위에 언급하였듯이, patterning 과정에서 원치 않은 부분을 제거하는 과정을 말합니다.

이 etching은 두 가지 종류가 있는데, 방향성이 둘의 가장 큰 차이점이 됩니다.

① Wet Etching : 용액을 사용하여 모든 방향으로 퍼지는, 등방성(isotropic etching)을 가지는 etching과정.

장) 속도가 빠름.

단) scaling이 되면서, 원하는 형태를 제작하기 어려워짐. 미세 공정에서는 사용 불가.

② Dry Etching : 기체를 사용하여 방향성을 가진, anisotropic etching을 함.

장) 원하는 형태를 형성하는데 더욱 뛰어남.

단) 느린 속도. 표면을 물리적으로 때리기 때문에, 과도한 etching이 일어날 수 있음.

5. Doping

부분적으로 원하는 Si type을 형성하기 위해 doping이라는 작업을 하고, 두 가지 방법을 사용합니다.

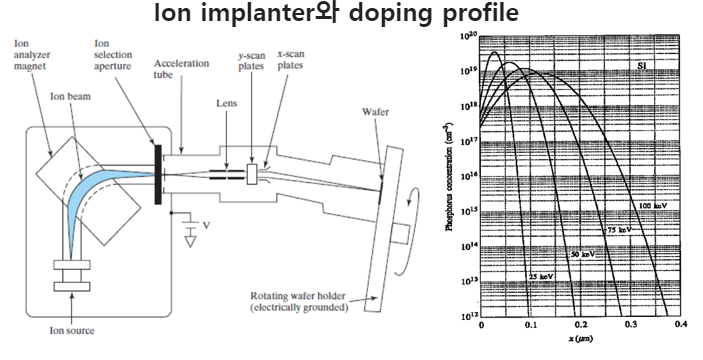

① Ion Implantation

mask가 없는 Si 영역에 dopant ion을 이용해 표면을 충돌시켜 doping하는 과정.

n-type은 P(Phosphorus), p-type은 B(Boron)을 사용.

장) 정확한 junction 형태 형성

단) 높은 에너지를 사용함으로써 격자가 무너져 crystalline 특성이 떨어질 수 있음.

ion을 표면에 충돌시킨 후 annealing으로 깊이를 control하고 후처리를 함.

dopoing profile은 가우시안 형태를 띔

└> 높은 에너지를 사용할수록 더 깊은 doping형태를 띄고, peak값은 감소하게됨.

② Diffusion

표면에 initial 물질을 일정량 도포시켜 annealing을 통해 농도를 확산시키는 doping 과정.

doping profile은 시간에 따라 달라지는 함수 형태를 가짐.

표면에서 방향성이 없는 랜덤한 방향으로 퍼지는 특성을 가짐.

장) deep junction 형성 가능.

단) 원치 않은 형태가 나올 수 있기에 미세 patterning에 부적합함.

온도가 높을수록 빠르게 진행되고, 높은 온도에 오랜 시간 진행하면 deep junction을 형성할 수 있고,

낮은 온도와 짧은 시간을 가하면 shallow junction을 형성할 수 있음.

열 공정 이후에 진행되면 x_j가 더 깊어질 수 있기 때문에, thermal budget을 고려해하 함.

6. Thin Film Deposition

IC(integrated circuit)에 필요한 thin film을 형성하는 과정으로 아래와 같은 형태를 만들 수 있습니다.

- poly-Si : gate

- metal layer : interconnects

- dielectric : metal layer 사이 형성

- IC의 encapsulation : IC 형성 후 외부 물질 차단

이러한 thin film을 형성하는 방법은 두 가지 존재합니다.

① Thermal evaporation

② E-beam evaporation

evaporation 과정은 vacuum chamber에서 source metal을 가열시키면 고체가 기화되며 wafer에 증착되는 방식을 가진다.

source를 가열시키기 때문에 wafer에 영향이 없게 둘 사이에 최소한의 거리가 필요하고,

thickness control을 위해 monitor를 내부에 설치해 이를 확인한다.

장) um의 단위를 사용하기에 patterning에 용이함.

단) 높은 cost를 가짐.

③ Sputtering

vacuum chamber에서 물리적으로 deposition하는 방법입니다.

plasma (+) 이온에 전압을 인가해 방향성을 가지고 가속시켜 target물질을 때리면, 이 힘으로 인해 target물질이 wafer에 deposit되게 됩니다.

④ CVD (Chemical Vapor Deposition)

두 가지 gas 물질을 하나로 만들어 deposition할 수 있는 방법으로, poly-Si, nitride, gate oxide를 형성합니다.

⑤ Epitaxial Growth

기판 위에 single-crystalline film을 형성하기 위해, lattice constant를 비슷하게 맞추어 진행하는 과정을 말합니다.

7. CMP(Chemical Mechanical Polishing)

각 공정을 진행하면서 표면을 평평하게 갈아주는 공정을 CMP라고 합니다.

화학적 용액인 slurry를 이용하여 물리적으로 압력을 가하고 돌려주어 평평하게 표면을 갈아줄 수 있습니다.

< Back-End Process >

앞의 공정을 진행한 뒤 진행하는 후공정 과정입니다.

- Interconnection 형성

└> via와 level을 연결하는 과정

└> silicide는 metal과 Si를 연결할 때 schottky barrier contact를 막아주는 역할을 함.

- testing

- die sorting

- packaging

.

.

.

과 같은 과정을 진행합니다.

오늘 게시글은 여기까지입니다!

다음 글은 CMOS에 대한 이야기와 CMOS 공정 흐름에 대해 다루어 보겠습니다!!

감사합니다 :)

'[학부 일기] 전자공학과 전공 > 반도체 공정 및 응용' 카테고리의 다른 글

| [반도체공정및응용] Oxidation (1) | 2023.02.22 |

|---|---|

| [반도체공정및응용] Photolithography (2) (0) | 2023.02.06 |

| [반도체공정및응용] Photolithography (1) (0) | 2023.02.06 |

| [반도체 공정 및 응용] Wafer&Cleaning (0) | 2023.01.09 |

| [반도체 공정 및 응용] CMOS Process Flow (0) | 2022.12.25 |