안녕하세요!

이번 게시글은 CMOS의 동작을 간단하게 살펴본 뒤, CMOS 공정 흐름을 알아보겠습니다!

마지막에는 NMOS의 공정 과정에 대해서도 아주 간단히 살펴보겠습니다.

< MOSFET과 CMOS >

우선 MOSFET은 NMOS와 PMOS로 나눌 수 있습니다.

MOS는 metal-oxide-semiconductor의 구조로 이루어진 것을 말하고,

NMOS는 gate에 V_th보다 높은 전압을 걸어주면 channel이 형성되면서(inversion) 전류가 흐르게 되고,

PMOS는 gate에 │V_th│보다 높은 전압을 걸어주게 되면 전류가 흐르게 됩니다.

(자세한 MOSFET에 대한 내용은 물리전자2 게시물로 가면 확인할 수 있습니다 :) )

이러한 NMOS와 PMOS를 combine하여 만든 것이 CMOS(Complemetry MOS)가 됩니다.

device가 switching되면서 전류가 흐르게 되기에, leakage가 없어 전력소모가 매우 낮습니다.

이러한 CMOS는 다양한 형태로 존재합니다.

기본적인 CMOS구조인 inverter는 3개의 terminal, Gate&Source&Drain 을 가집니다.

그리고 전체적인 device 형태를 가진 silicon wafer와 배선들을 연결해주는 interconnection layer로 구분되어 집니다.

< Cross-Section of IC Chips >

전체적인 IC Chip의 형태를 보여줍니다. 각 부분에 대해서는 이후에 설명될 것 같습니다!

< IC Manufacturing Process >

이러한 IC Chip을 만드는 과정은 크게 4단계로 분류됩니다.

Design → Wafer fabrication → Assembly → Test

위와 같이 schemetic과 layout을 디자인하면 wafer에 공정을 시작하게 됩니다.

아래에서 언급될 내용들은 Design과 Wafer fabrication 부분이 되겠습니다.

우선 가장 대표적인 CMOS Inverter의 schemetic과 layout은 아래와 같습니다.

여기서 만들어주는 active region은 channel을 doping하는 과정입니다.

원하는 V_th를 형성하기 위해서 제작합니다.

이러한 layout은 다음과 같은 mask를 이용하여 제작하게 됩니다.

검정색 부분은 막혀있는 부분, 흰색 부분은 뚫려있는 부분입니다.

각각의 마스크는 뒤에서도 사용될 예정이니 차차 설명하겠습니다.

< CMOS Process >

CMOS를 만드는 과정은 다음과 같습니다.

~~~~ FEOL(Frontend of the Line) ~~~~

① Actice Region Formation

active region은 mos로써 동작하는 영역을 만들어주는 과정입니다.

100 crystalline 구조, 5-50의 저항도를 가진 p-Si 기판입니다.

이 위에 pad oxide인 SiO2를 쌓아줍니다.

이는 질은 별로지만 빠르게 올려주는 oxide입니다.

그리고 이후 공정에서 사용될 insulator인 Si3N4를 쌓고,

PR을 spin coating을 이용해 올려줍니다.

Mask #1

actice area를 지정해주는 mask #1를 이용하여 영역을 지정해줍니다.

이때 nitride(Si3N4)는 dry etching을 진행합니다.

그리고 LOCOS를 형성하는 과정을 진행합니다.

Field oxide로 동작하는 LOCOS는 고온에서 H2O를 가열시켜, 노출된 부분이 부풀면서 형성됩니다.

이는 새 부리처럼 부풀면서 actice area가 줄어드는 Bird's beak 문제를 보여 이를 보완하기위해 현재는 STI를 사용합니다.

STI(Shallow Trench Isolation)은 소자↓, 집적도↑ 으로 생기는 전기적 간섭을 없애주는 절연체 물질을 말합니다.

즉 소자를 전기적으로 서로 분리시켜는 역할을 합니다.

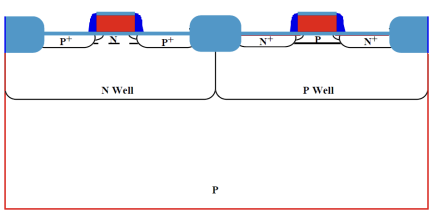

② N&P Well Formation

Mask #2

Mask #2를 사용하여 B+를 implant해 줍니다.

B+는 P-well을 형성하고,

저농도로 도핑함으로써 body 부분을 형성해줍니다.

( N = 10^13 cm-3 , E = 150-200keV )

Mask #3

Mask #3를 사용하여 P+를 implant해 줍니다.

P+는 N-well을 형성하고,

저농도로 도핑함으로써 body 부분을 형성해줍니다.

( N = 10^13 cm-3 , E = 300+keV )

PR을 제거한 뒤, 높은 온도에서 drive-in을 진행합니다.

ion implantation이후 가열하여 depletion시키는 과정으로,

well depth 형성, repair damege을 하게 됩니다.

(4-6 hours, 1000-1100 ℃ )

소자의 size가 작아지면서 thermal budget이 존재하기 때문에,

높은 온도에서 빠른 RTA(Rapid Thermal Anneal)를 진행합니다.

③ Gate Formation - Channel Implantation

Mask #4

원하는 V_th를 형성하기 위해 channel 영역을 doping합니다.

정확한 doping을 위해 B을 낮은 에너지로 implant 합니다.

( N = 1-5 X 10^12 cm-2 , E = 50-75 keV )

Mask #5

As를 낮은 에너지로 implant 합니다.

( N = 1-5 X 10^12 cm-2 , E = 75-100 keV )

④ Gate Formation - Gate Oxide and Poly-Si Deposition

새로운 gate oxide를 생성합니다.

기존의 pad oxide는 많은 damage를 받아서 성질이 변화했기에, 이를 없애고 새로운 oxide를 형성하여

gate oxide로 사용하게 됩니다.

LPCVD를 사용해 poly Silicon gate를 deposition합니다.

~0.5um의 두께를 만들기 위해 mask없이

고동도의 P+나 As+(5 X 10^15 cm-3)를 implant합니다.

⑥ Gate Formation - Gate Patterning

Mask #6

channel length를 결정해주는 gate를 patterning하기 위해

mask #6을 사용합니다.

anisotropic etch로 정확한 형태로 poly-Si를 etch합니다.

아래는 형성된 MOS구조를 TEM을 사용해 관찰한 것입니다.

전체적으로 균일한 Si과 부분적으로 균일한 Poly-Si, 불규칙(비정질)한 SiO2를 관찰할 수 있습니다.

⑥ Tip or Extension(LDD) Formation

Mask #7

LDD(Lightly Doped Drain) or SDE를 impant하는 과정입니다.

channel의 길이가 짧아질수록 커지는 Energy로 인해 생기는 oxide 파괴를 막기 위해 이를 사용합니다.

NMOS에는 P를 doping해 줍니다.

(N = 5 X 10^13 cm-3 , E = 50keV )

Mask #8

LDD를 implant하기 위해 B를 doping해 줍니다.

(N = 5 X 10^13 , E = 50keV )

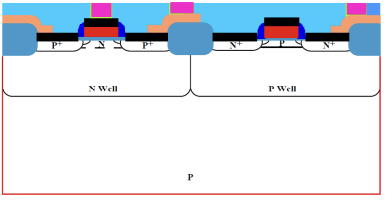

⑦ Source/Drain Formation - Sidewall Spacer

Sidewall은 LDD영역을 추후 Source, Drain 형성에 진행될 고농도 doping에 의한 damage를 막기 위해 진행합니다.

균일하게 SiO2를 전체적으로 deposition합니다.

anisotropic etching으로 sidewall spacer를 형성합니다.

(전체적으로 균일하게 없애면 sidewall만 남음)

⑧ Source/Drain Formation - S/D Impantation

Mask #9

NMOS의 Source와 Drain 형성을 위해

고농도의 As+를 implant합니다.

( N = 2-4 X 10^15 cm-2 , E = 75 keV )

Mask #10

PMOS의 Source와 Drain 형성을 위해

고농도의 B+를 implant합니다.

( N = 1-3 X 10^15 cm-2 , E = 50 keV )

⑨ Source/Drain Formation - RTA

최종적으로 depth를 결정하고 repair를 위해

RTA를 진행합니다.

~~~~ Backend of the Line) ~~~~

⑩ Contact and Local Interconnect Formation

mask없이 전체적으로 oxide를 etch해 줍니다.

Ti를 전체적으로 deposite 합니다.

Silicide를 전체적으로 형성하여 contact 이전에 pad를 만듭니다.

ⅰ) Si 인 곳 - Ti와 반응

온도를 가열하면 TiSi2(Silicide) 형성

ⅱ ) Si가 아닌 곳 - N2와 반응

온도를 가열하면 TiN(nitride) 절연막으로 변환됨

Mask #11

Mask를 사용하여 contact부분의 TiN를 etching합니다.

즉, local interconnection을 형성하게 됩니다.

⑪ Multilevel Metal Formation - SiO2 Deposition & CMP

metal끼리의 간섭을 없게 하기 위해 SiO2 layer를 형성해줍니다.

CMP를 사용해 평탄화를 진행합니다.

(Chemical-Mechanical Polishing)

Mask #12

mask를 사용하여 contact 부분을 patterning해 줍니다.

SiO2를 etching합니다.

W를 CVD deposition하여 via를 형성합니다.

CMP를 통해 표면을 깎아줍니다.

Mask #13

Al를 deposition한 뒤 원하는 부분만을 etching,

이를 통해 metal 1을 형성합니다.

위의 metal형성 방법을 통해 level과 via를 반복하여 형성하면 다음과 같은 CMOS를 형성할 수 있습니다.

최종적으로 ILD(Interlayer dielectric)을 deposite하여 각 metal의 간섭을 최소화 합니다.

+ 추가적 보충 내용 +

< NMOS Process >

이건.. 제 수업 때 퀴즈에 나왔던 최소한의 mask를 가지고 만드는 nmos prcoss 과정입니다.

< CAD 프로그램을 사용한 TFT Mask Layout >

이건 수업에 진행하였던 과제입니다.

CAD 프로그램을 사용하여 TFT(thin film transistor)를 제작하였고, 여기서 NMOS를 만들었습니다.

위는 nmos의 transistor입니다. 사실 각각의 마스크를 따로따로 보면, 구조가 더욱 확실해 보입니다.

이 내용은 나중에 시간이 된다면 따로 게시글로 올리고 싶네요..!!

오늘 글은 여기까지 입니다!

사실 공정 과정은 사람마다 다르게 진행할 수 있으니 참고하여 이런 과정을 해야하는구나~ 가 가장 중요한 것 같네요.

다음 글 부터는 반도체 공정에 대해 하나하나 살펴볼 예정입니다.

많이 부족한 글 읽어주셔서 갑사합니다 :)

'[학부 일기] 전자공학과 전공 > 반도체 공정 및 응용' 카테고리의 다른 글

| [반도체공정및응용] Oxidation (0) | 2023.02.22 |

|---|---|

| [반도체공정및응용] Photolithography (2) (0) | 2023.02.06 |

| [반도체공정및응용] Photolithography (1) (0) | 2023.02.06 |

| [반도체 공정 및 응용] Wafer&Cleaning (0) | 2023.01.09 |

| [반도체 공정 및 응용] Semiconductor Fabrication & Applications (0) | 2022.12.18 |