안녕하세요!

오늘은 반도체 공정 및 응용의 Interconnection에 대한 글을 써보려 합니다!

오늘 글은 수식은 없지만 내용과 사진이 많아 길어질 것 같아요..!ㅜ

- Interconnections in IC chip

interconnection은 다음과 같이 IC chip에서 적용됩니다.

IC에 사용되는 common interconnection 물질은 다음 세가지가 있습니다.

- Al : 증착이 쉬워 쉽게 올릴 수 있고, etching이 쉬움

- poly-Si : Si와 WorkFunction 차이가 적어 ohmic contact가 작기 때문에 loss가 적음

- diffusion regions : 같은 영역으로 도핑

각각은 사용처에 따라 cross over되고 density 향상이 목표점입니다.

이러한 interconnection 물질은 낮은 sheet resistance를 가져야만 합니다.

voltage drop과 propagation delay를 최소화 시켜 RC delay를 최소화 해야하기 때문입니다.

그리고 line끼리 분리시키는 SiO2와의 반응성이 없어야 하고, Low-R ohmic contact를 필요로 합니다.

long term operation이어야 하기에 효율, 수명, manufacturing이 중요시 됩니다.

- Metal Interconnections & Contact Technology

기술의 발전으로 앞의 세 interconnection에 적용되는 물질도 변화하였습니다.

- gate metal : Au / Al -> poly Si -> deped poly Si -> polycide or silicide

- interconnection metal : Al -> AlCu / Cu

- Barrier metals : TiN(Al/Si) -> TiW(Al/Silicide), TaN(Cu/low-k dielectric)

각 물질에 대해 알아보겠습니다!

¤ Au : 높은 확산성으로 전도도가 좋고, Si에 deep-level recombination center를 생성

recombination center가 energy band gap 내부에 생성되면 e-가 갇히고 시간이 지나면 h+와 만나 recombination되어 없어짐

- free radical의 lifetime감소

- chip packaging에 널리 사용

¤ Al : 저렴하고 낮은 저항성으로 conductivity가 좋고 SiO2에 잘붙음

- junction spiking & electromigration 문제가 있음

¤ poly-Si : stability가 좋고 P, anitimony와 doping가능

- resistivity가 감소하며 contact에 문제가 없고 저항이 거의 없음

- 전도도가 낮고 형성이 어려우며 속도가 느림

¤ Silicide : metal(TiSi2, CoSi)과 stable metallic, semiconduction의 compound 형성

- 낮은 resistivity, 좋은 thermal stability

- gate electrode로 사용 가능

¤ Cu : 낮은 resistivity, 적은 elegromigration

- etching 시 issue 발생, adhesion SiO2가 별로여서 전기적 분리가 어려움

- damascene process를 사용 (interconnecting Cu, low-k dielectric)

- Ohmic Contact Formation

ohmic contact는 아래 그림과 물리전자 게시글에서 더 자세하게 확인해주세요!

< Aluminum-Silicon Eutectic >

- Al behavior

Si는 1412℃에서 녹고 pure한 Al는 660℃에서 녹는점을 가집니다.

Si와 Al를 ixture하면 eutectic characteristics => T_melt < 660℃여야 합니다.

minimum melting(eutetic) temtrature는 Al-88.7%, Si-11.3%가 함량되어있을 때 577℃가 됩니다.

결론적으로, Al 공정은 모든 고온 process를 한 후에 진행해야 합니다!

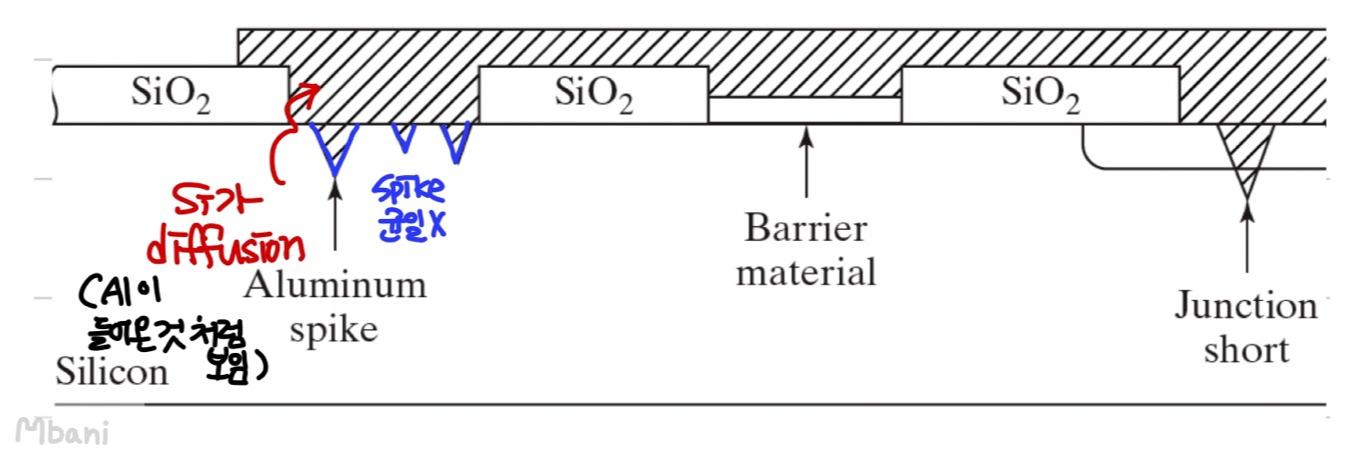

- Aluminum Spiking & Junction Penetration

contact formation을 좋게 하기 위해 보통 Al은 450~500℃에서 inert atmosphere로 annealing을 진행해줍니다.

이때 Si와 Al의 반응성이 좋아 Si가 Al로 diffusion되는 현상이 발생하게 됩니다.

shallow junction의 경우 Si에 Al contact이 형성되는데, 흡수된 Si 양은 시간, 온도, contact크기에 의존합니다.

이렇게 흡수가 not uniform하게 된 현상을 Al spike & penetrate Si 라 합니다.

그리고 n-type Si을 사용할 때 아래의 문제점들이 발생합니다.

① 표면적의 증가로 IV curve 예측이 어려워짐

② 표면적의 증가로 R이 증가해 curve가 아래로 내려감

③ 고농도 표면 doping으로 인해 ohmic이 깨져 특성이 바뀜

이러한 문제점들을 해결하는 방법은

① deposition 동안 Al film에 1%의 Si를 추가

-> diffusion은 농도차이에 의해 발생하므로 추가한 Si가 이 차이를 줄여줌

② polysilicon thin film이나 metal(TiN, Pt, W)로 barrier layer를 deposit해줌

- Contact Resistance

낮을수록 좋은 contact resistance는 두 물질 사이의 ohmic contact와 관련된 작은 resistance를 말합니다.

아래 그래프를 통해 물질간의 resistance를 확인할 수 있습니다.

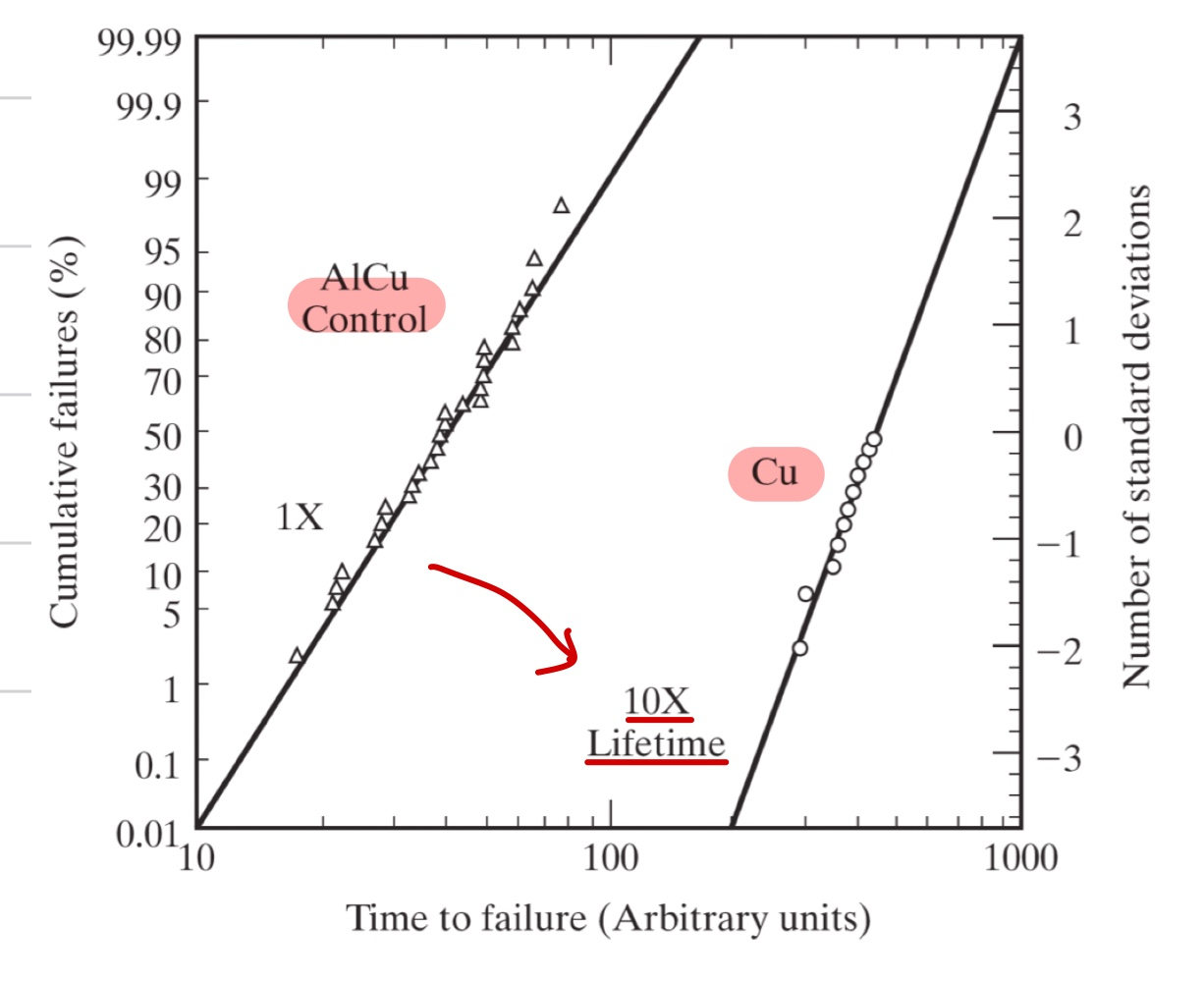

- Electromigration

전자의 운동량 전달(momentum transfer)로 인한 metal film에서 atom이 이동하게 됩니다.

이때 high-current density 상황에서 metal-atom의 movement가 초래하는 상황을 electromigration이라 합니다.

void는 open circuit을 형성하고 metal pileup(hilocks)는 short circuit을 만듭니다.

pileup이 커지면 metal line이 short 되는 현상은 아래 그림에서 확인할 수 있습니다.

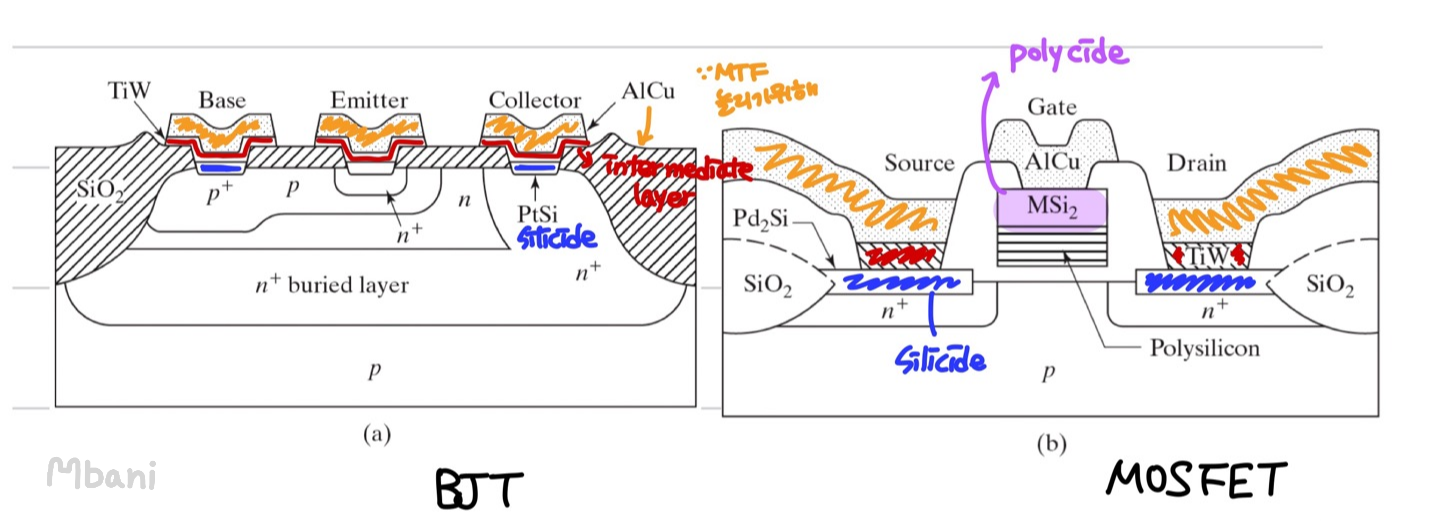

electromigration으로 인해 MTF(mean time to failure)은 실험적으로 cureent density J, 온도와 관련이 있음을 수식적으로 나타내면 아래와 같습니다.

Al electromigation을 없애기 위한 solution으로,

small percentage of a heavier metal such as Cu 나 Cu를 추가하면 위 현상을 막을 수 있습니다.

sputter deposition을 하면 Al 95%, Cu 4%, Si 1%를 사용하면 큰 효과를 낼 수 있습니다.

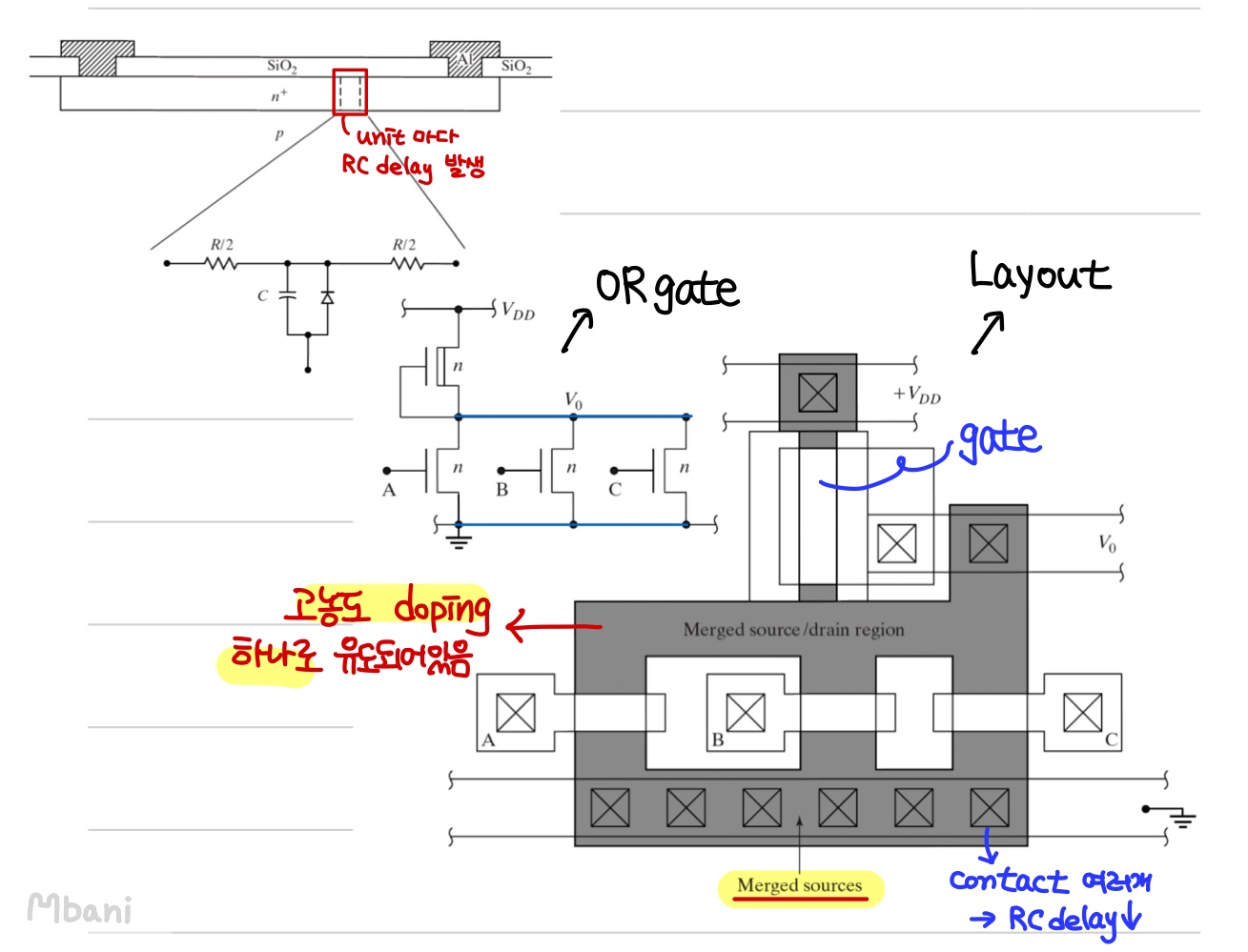

< Diffused Interconnections >

긴 diffused line에는 큰 RC delay가 초래됩니다.

RC time은 operating frquency를 제한시켜 줄여야 합니다.

multiple contact는 constant resistance를 줄이기 위해 사용합니다.

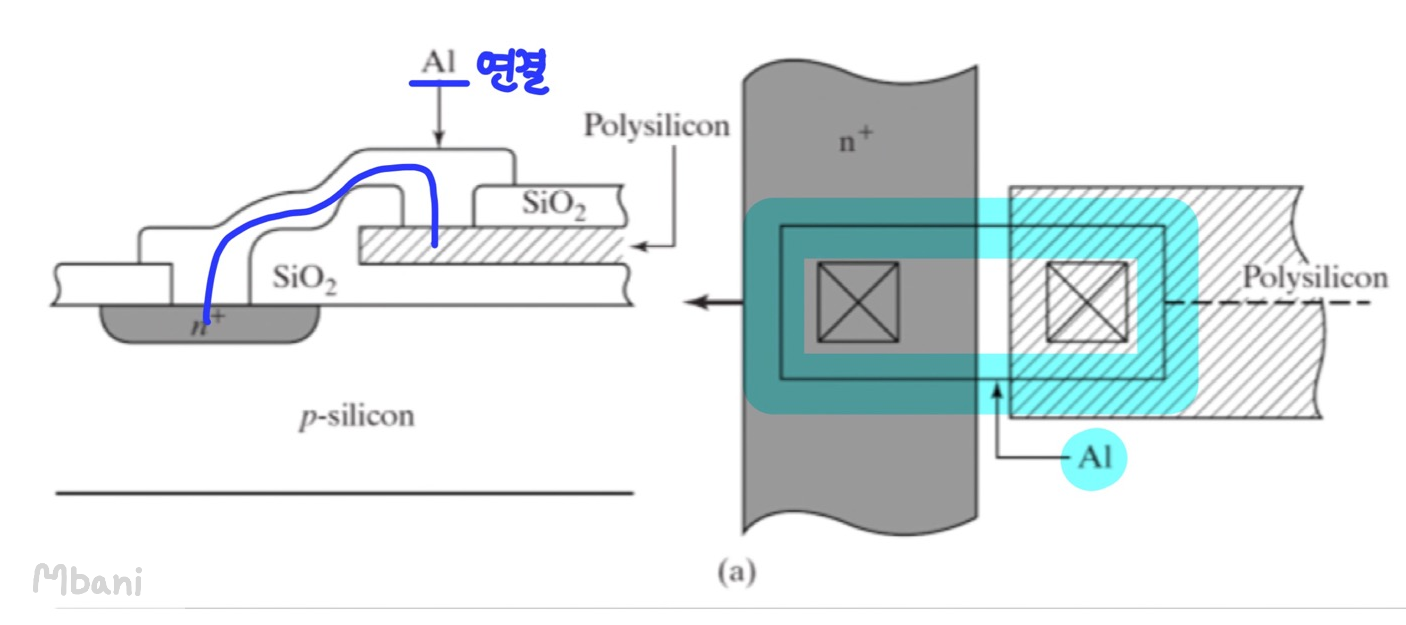

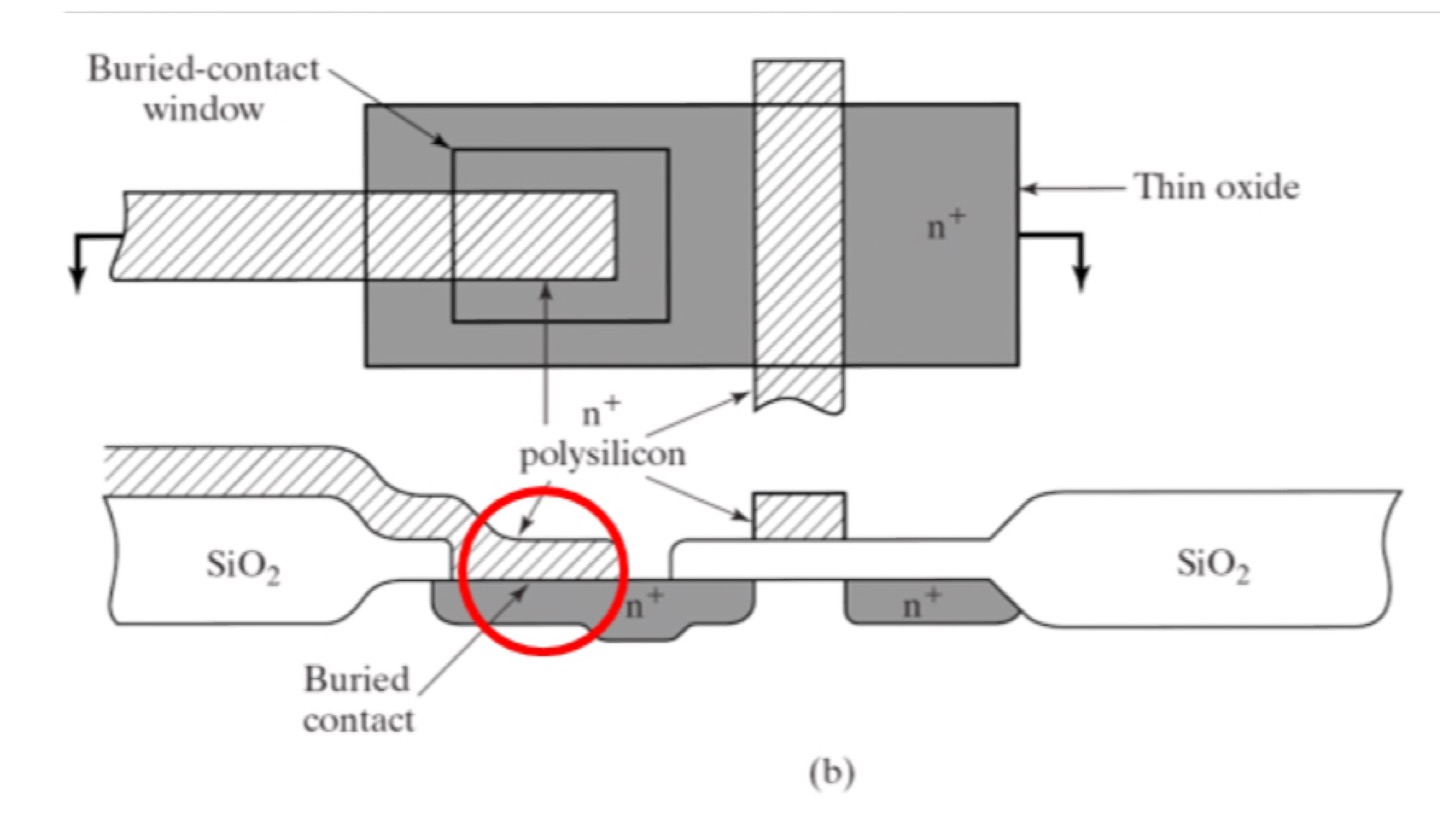

- Interconnecting poly-Si & n+ Diffusion

위 그림은 ohmic contact가 형성되지 않고 junction spiking의 문제가 발생할 수 있습니다.

이를 해결하기 위해 diffusion과 바로 연결되는 polySilicon을 burried contact로 막을 수 있습니다.

이렇게 되면 direct연결이 Al가 아니기 때문에 junction spiking이 형성되지 않지만

mask를 또 사용해야 하기에 공정 비용이 증가하게 됩니다.

이러한 문제는 Al overlap을 통해 butted contact를 형성시켜줄 수도 있습니다.

- Silicide, Polycide, Salicide

1) Silicide : Si와 복합체가 된 metal의 wide range를 말합니다.

장점으로는 junction spiking이 낮고 sheet resistance도 낮습니다.

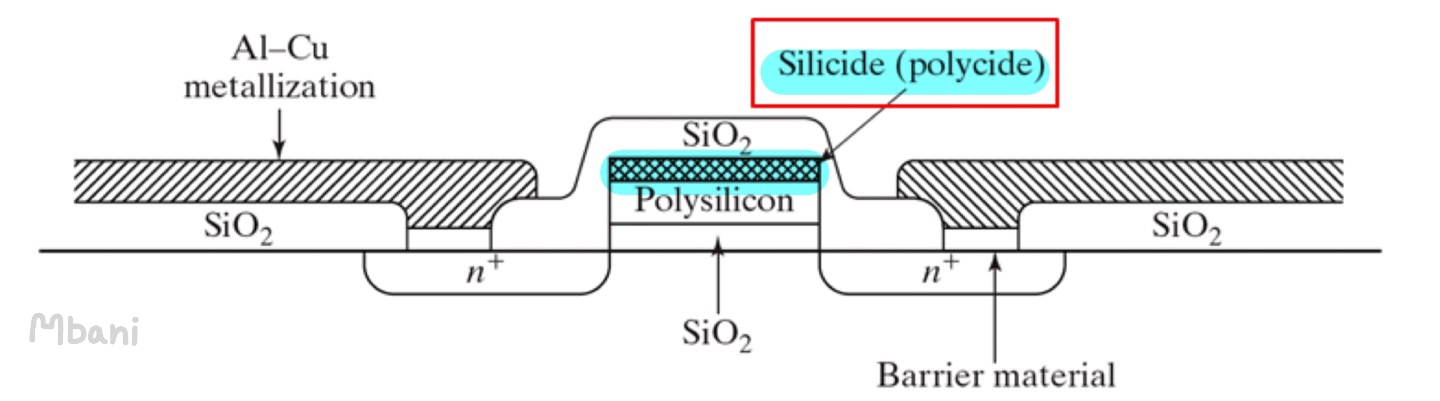

2) Polycide : poly-Si gate위에 형성된 silicide를 말합니다.

600-1000℃에서 heated하면 15-50uΩ-cm의 낮은 resistivity를 형성합니다.

3) Salicide : self-sligned silicide를 말합니다.

silicide는 sintering동안 metal과 silicon,polysilicon이 접촉되는 영역에만 형성되게 됩니다.

mask없이 접촉된 부분에만 가열되며 자동적으로 형성되는게 salicide입니다.

즉, 이 물질들은 Al spiking을 막아주고 반응 부분만 compound로, 나머지는 선택적으로 날려주게 됩니다.

- Barrier Metals & Multilayer contacts

Silicide와의 직접적인 Al contact도 pitting, spiking 문제를 겪습니다...

Si diffusion을 막기위한 가장 효과적인 방법은

metal(TiW)의 Interconnection layer를 사용하면 high permaformance를 만들어낼 수 있습니다.

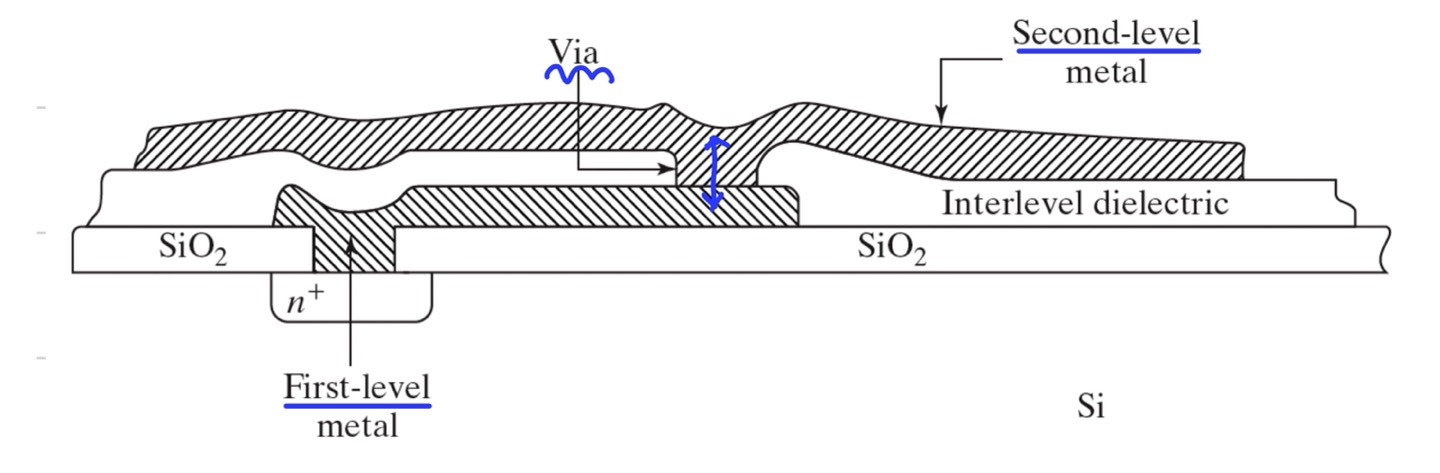

< Multilevel Metallization >

metal의 single level은 전체를 제공하기 않기 때문에 poly-Si의 2/3 level을 각 층에 metallization을 해줍니다.

이 level들은 wirability와 adequate power distribution을 제공합니다.

basic multilevel metallization은 다음과 같습니다.

- metal의 1st level을 deposition & patterning

-> 1st layer에 inter level dielectric dielectirc deposite

-> dielectric layer는 좋은 step coverage를 제공하고 smooth한 topology를 도움

-> 기둥인 via를 만들고 2nd level of metallization deposition & patterning -> ...

- 과정 진행 후 planarized metallization으로 평탄화. 높은 planar layer에서 CMP를 사용

- via(W)는 filling사용

- dielectric deposition -> metallization -> CMP process 순으로 진행

- Electroplated Copper Interconnect

Cu는 low resistivity를 가지고 싸고 많은 양을 보입니다.

deep-level impurity와 Si에 빠르게 diffuse되기 때문에 Si substrate와 device 오염에 각별해야 합니다.

또한 dry etching 사용이 불가능해 additive plating techniques를 사용해야 합니다.

copper를 plate하는 방법은 아래와 같습니다.

- seed layer deposition(보호목적)

-> mask로 PR deposited&patterned

-> wafer에 plating system(Cu solution)

-> masking layer 제거

이 방법은 planarity가 부족하기 때문에 아래의 damascene 방법을 주로 사용해 Cu를 형성합니다.

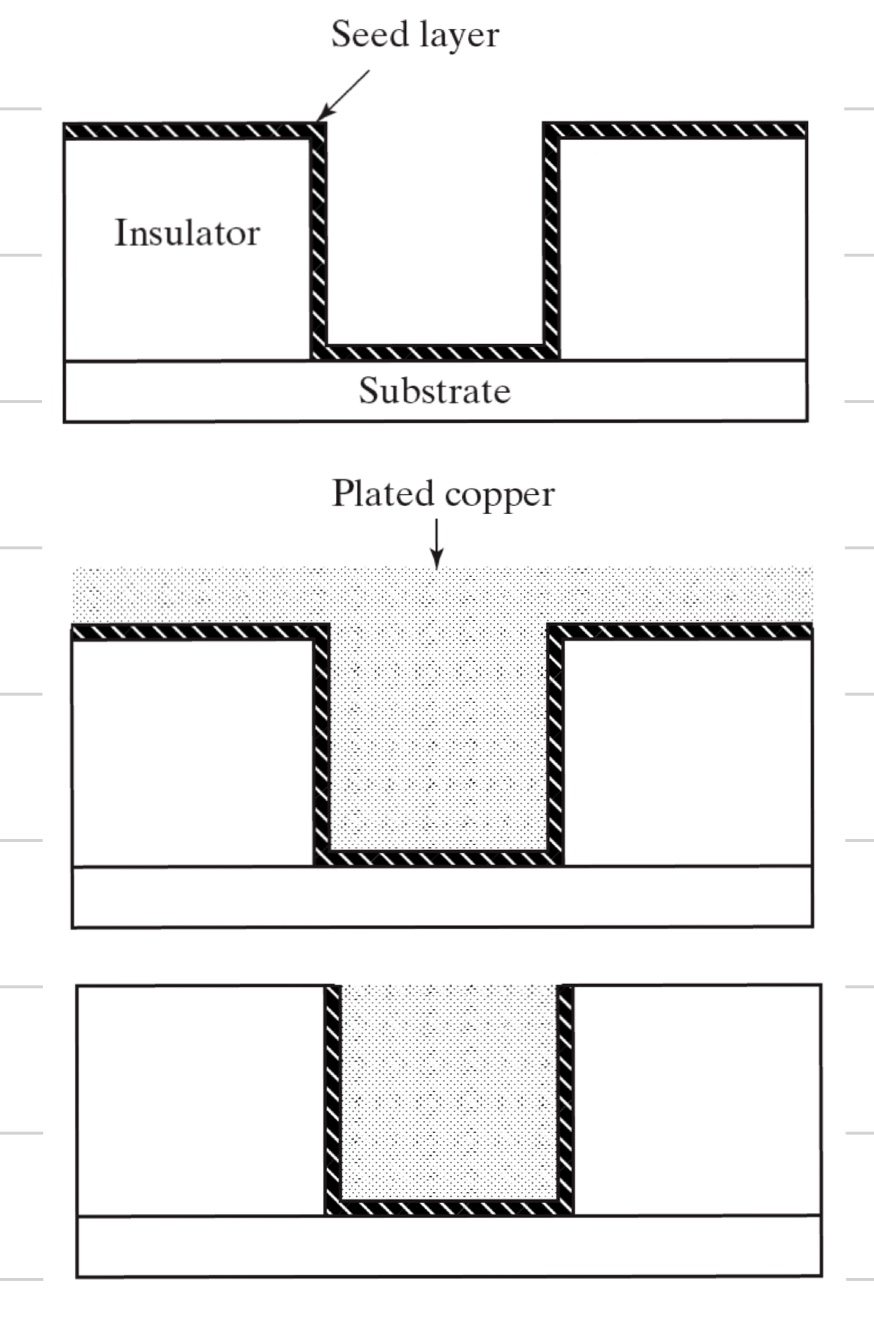

- Damascene Plating :

damascene 공정은 Si dioxide와 같은 insulating layer 기판 surface에 Cu로 deposited하는 방법입니다.

desired interconnect pattern을 만들 때, standard photolithography를 사용합니다.

과정) Si substrate 위 SiO2를 증착한 뒤 Seed layer 증착

-> Electrochemical deposition을 통해 Cu plating

-> CMP을 통해 윗면을 평탄화 하게 진행해줌

이 공정으로 Cu와 Si 간의 확산을 막고, void가 생겨도 전기적 연결이 끊기지 않게 하며, planarity가 우수해 집니다.

- Dual Damascene Structures

interconnection line과 via를 동시에 Cu로 제작하는 방식으로, damascene process를 두번 사용합니다.

오늘 글은 여기까지 입니다!

다음이 반도체 공정 및 응용의 마지막 게시글일 것 같아요..!!

감사합니다!

'[학부 일기] 전자공학과 전공 > 반도체 공정 및 응용' 카테고리의 다른 글

| [반도체공정및응용] Packaging (0) | 2023.03.22 |

|---|---|

| [반도체공정및응용] Etching (0) | 2023.03.01 |

| [반도체공정및응용] Deposition (0) | 2023.02.26 |

| [반도체공정및응용] Ion Implantation (0) | 2023.02.24 |

| [반도체공정및응용] Diffusion (0) | 2023.02.23 |