안녕하세요!

반도체 공정기술 교육원, SPTA에서 진행하는

'반도체 소자 제작 및 전기적 특성 분석(심화)'과정을 3/6(월)-3/9(목)동안 수강하였습니다.

최대한 오래 기억하고 싶어서 각 게시글은 수강한 당일날 작성해 수료 뒤 수정과정을 거쳐 올립니다!

각 과정별로 정리하는게 더 가시성이 좋을 것 같아서 이후 글 부터는 각 과정의 제목에 맞게 정리해 올리겠습니다.

Day 1 ) 전체적인 fabrication 과정에 대한 이론 수업과 poly-Si LPCVD 까지의 실습

< 이론 수업 >

먼저, 자기소개를 진행하였습니다.

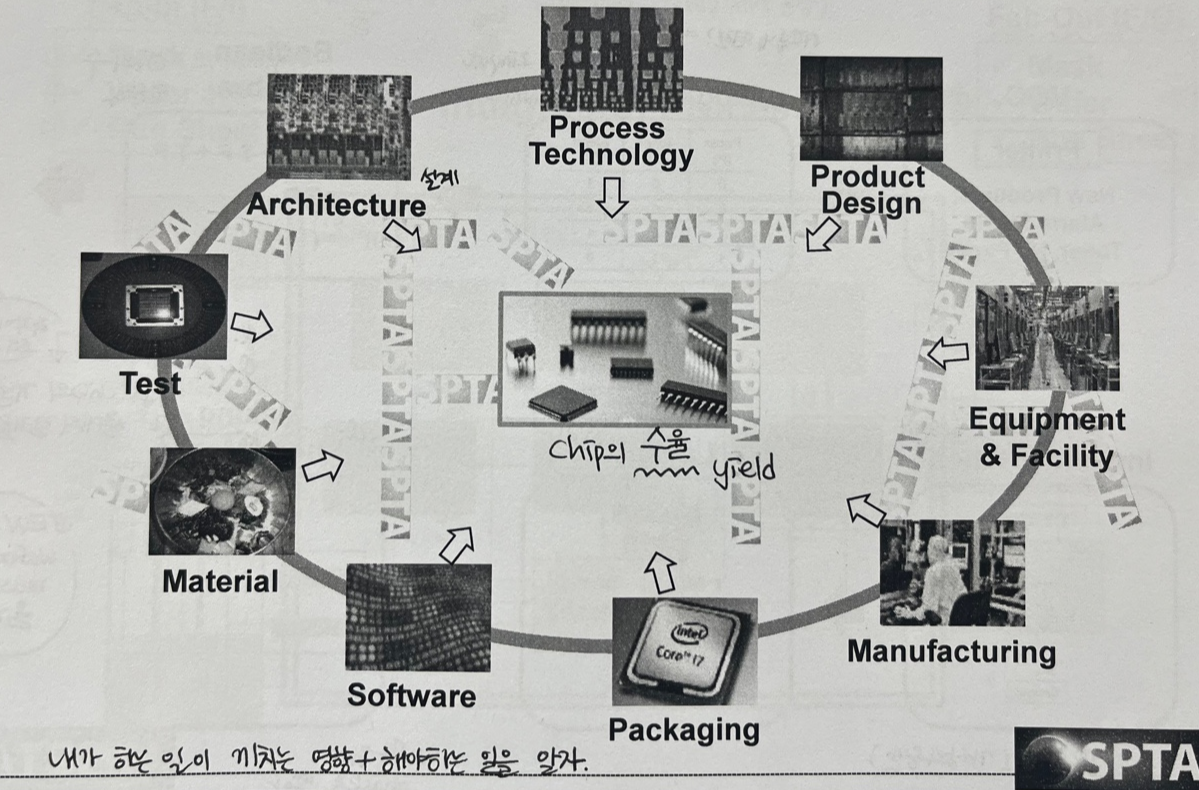

그리고 반도체 생태계, Eco System @Semiconductor Industry를 배웠습니다.

chip의 수율, yield 향상을 목표로 하여 많은 활동이 반도체 생태계를 이루고 있습니다.

교수님께서는 "내가 하는 일이 끼치는 영향과 해야하는 일이 뭔지 알고 하라"고 조언해 주셨습니다.

Semiconductor IC Flow는 다음과 같습니다.

Chip Design -> Fabrication -> Test & Package

Chip design은 VOC, Circuit Design, Layout, EDA tools을 사용하는 활동들이 속해있습니다.

이 디자인은 Photo Mask를 통해 Fabrication됩니다.

clean room, process tools, integration process, FEOL+BEOL, wafer level을 보이는게 Fabrication 단계입니다.

그리고 processed wafer를 통해 Test&Package를 진행하게 됩니다.

electrical test, EDS, wafer thinning to wire bonding, package level을 이 단계에서 진행하게 됩니다.

Fabrication의 1위는 삼성, Test&pacakge의 1위는 TSMC가 차지하고 있습니다.

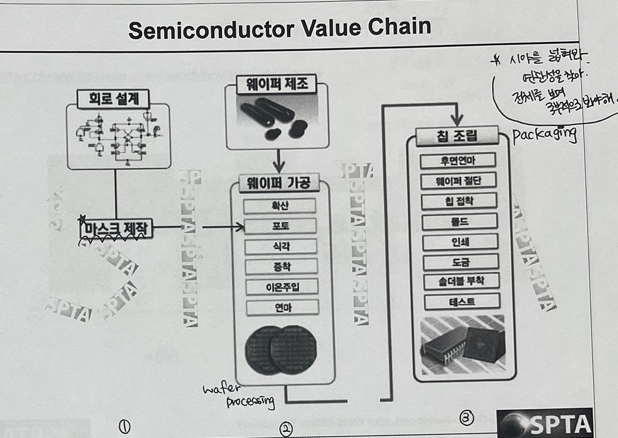

Semiconductor value chain을 살펴보면,

①mask, ②wafer processing, ③chip packaging 세 단계로 구성할 수 있습니다.

IC Fabrication에서는 Fab-In(F/I), Fab-Out(F/O)라는 용어를 사용합니다.

Fab-In은 mask의 pattern을 wafer위에 run sheet을 기반으로 제작합니다.

이를 '반도체=주상복합'이라 표현할 수 있습니다.

설계도면을 가지고 땅위에 순서대로 제작하는 line을 따르는 것으로 설명할 수 있죠.

Fab-Out을 하면 위 세가지를 가지고 나오게 됩니다.

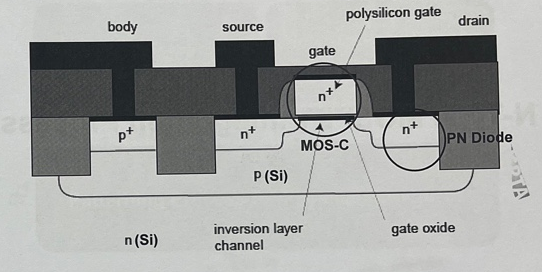

마지막으로 MOSFET에 대해 간단히 알아보았습니다.

mosfet의 정의는 다음과 같이 할 수 있습니다.

1. gate 아래에 inversion layer가 생기고,이는 gate voltage에 의존합니다.

2. 그리고 이 영역은 heavily-doped region이고, source와 drain과 연결되어 있습니다.

3. 4개의 terminal인 gate, source, drain, body로 구성되어 있습니다.

소자를 볼 때는 plane view와 virtical view를 같이 이해하는게 좋습니다.

MOSFET은 이름에서도 정의가 되어있습니다.

MOS/FE/T - MOS : metal-oxide semiconductor 구조를 기반으로

- FE : field effect를 동작 기본 원리로 하는, 전기적으로 중성을 보이는

- T : 전압에 따라 저항이 바뀌는 transistor 물질

이후 적을 게시물은 제 필기를 정리하는 용도로 간단한 문장들로 구성해 작성하려 합니다 ㅎㅎ

면접 준비를 하면서 하나하나 말로 풀어 설명해보는 연습도 꼭 해보려고요!

부족한 부분있으면 꼭 알려주세요 감사합니다!