이전 게시글과 이어집니다!

< 실습 과정 > Day 4 ) CV curve와 IV curve 측정

< 실습 과정 >

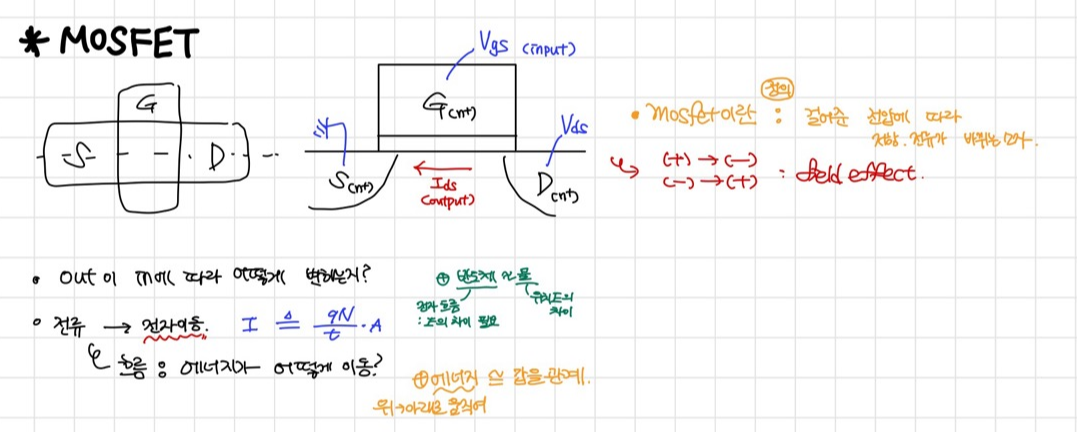

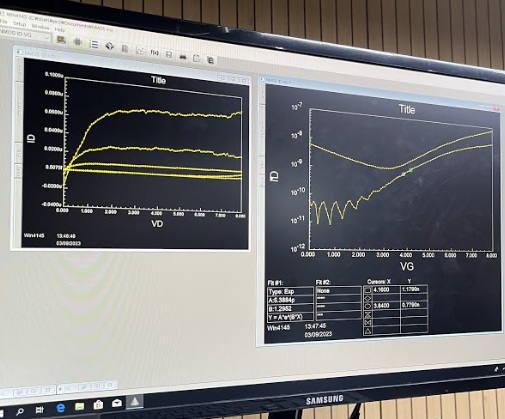

1. MOSFET

- MOSFET은 걸어준 전압에 따라 저항이 바뀌고 전류가 바뀌는 소자

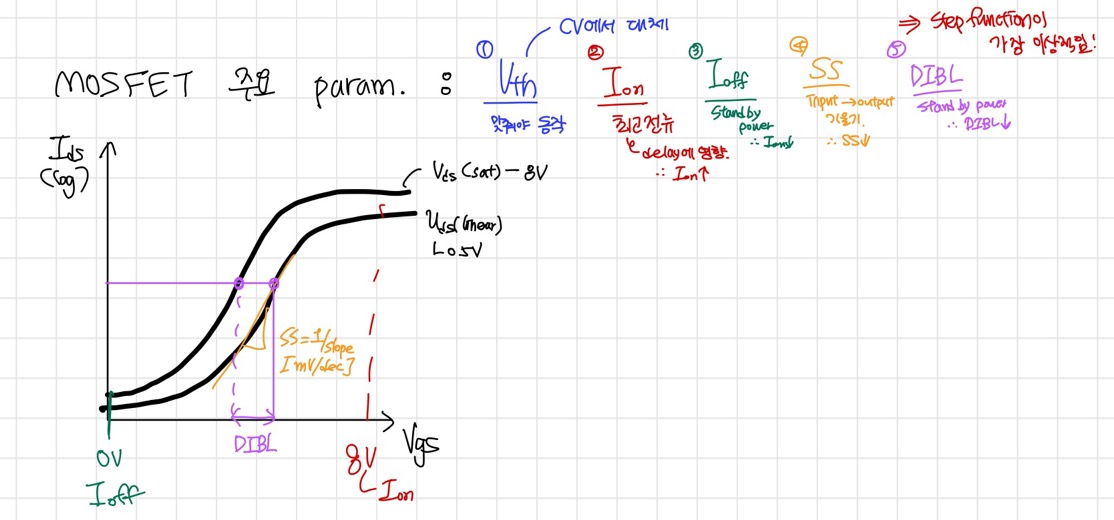

- IdVd 그래프와 IdVg그래프 범위별로 잘 알아둬야함.

- Vds는 carrier를 빼내고, carrier의 속도에 linear하게 영향을 끼침.

- IdVg 그래프에서 5가지 주요 parameter를 확인할 수 있고, 실험을 통해 확인할 것!

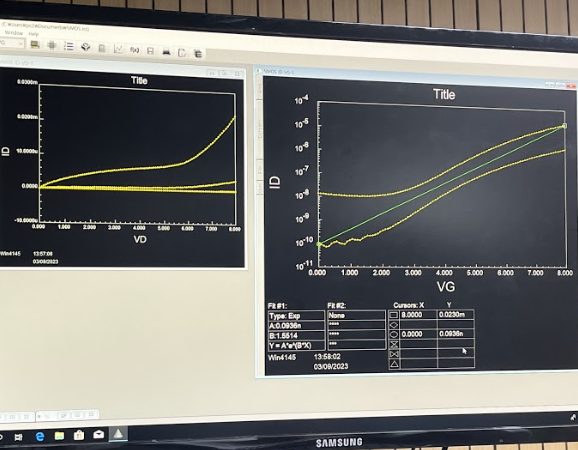

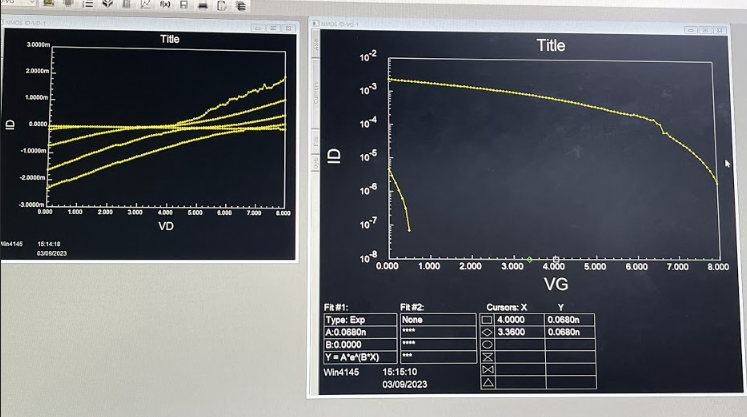

2. IV curve

- MOSFET에서 측정

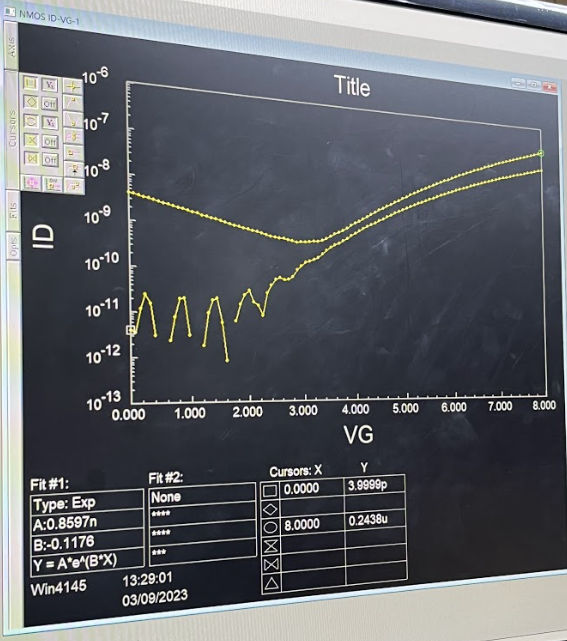

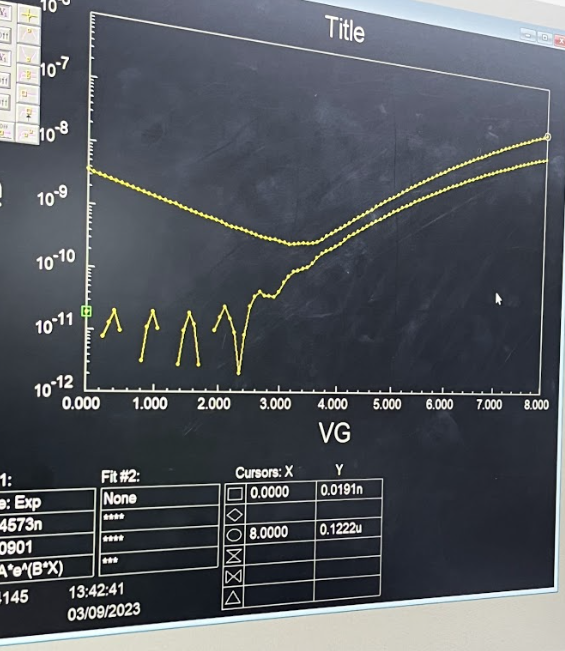

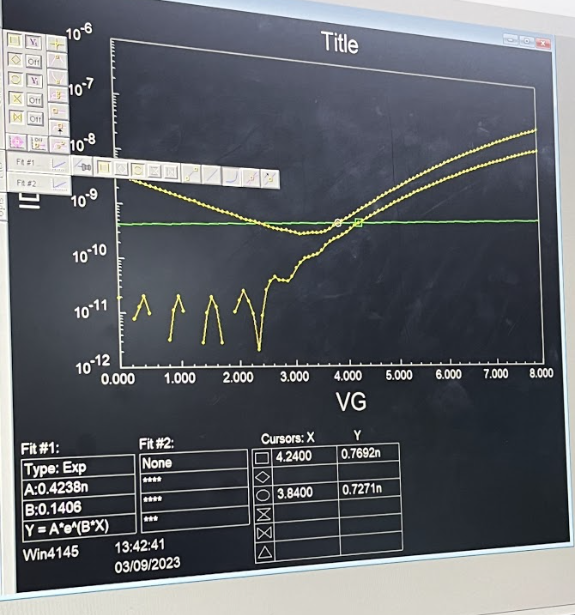

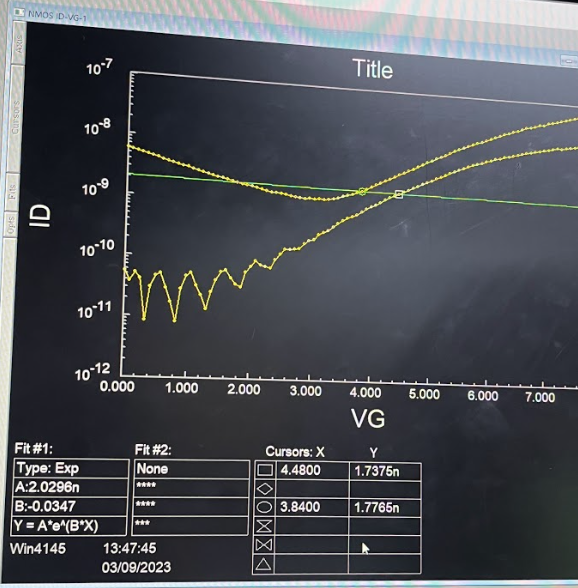

① 5번째 die ) W=100, L=100um

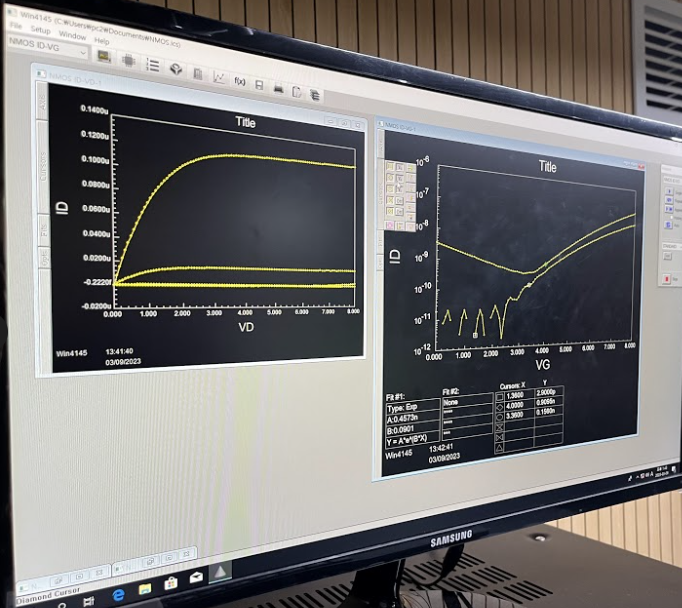

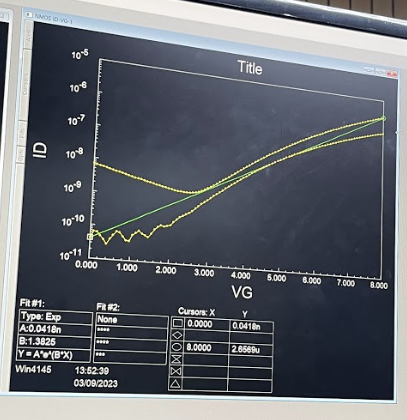

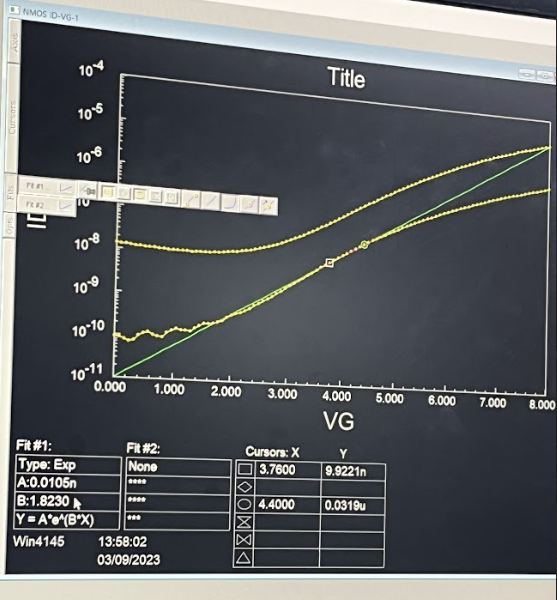

② 5번째 die ) W=100, L=70um

- Vth = 3.68V

- I_on = 0.1222uA

- I_off = 0.0191nA

- SS = 1/1.8475 = 0.54

- DIBL = 0.4V

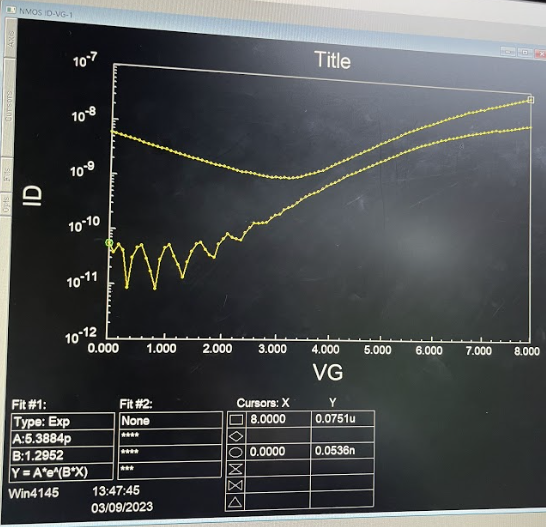

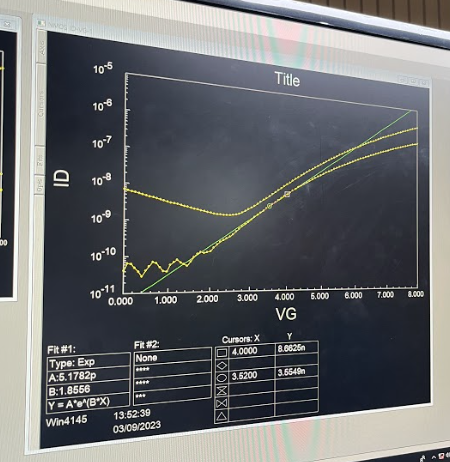

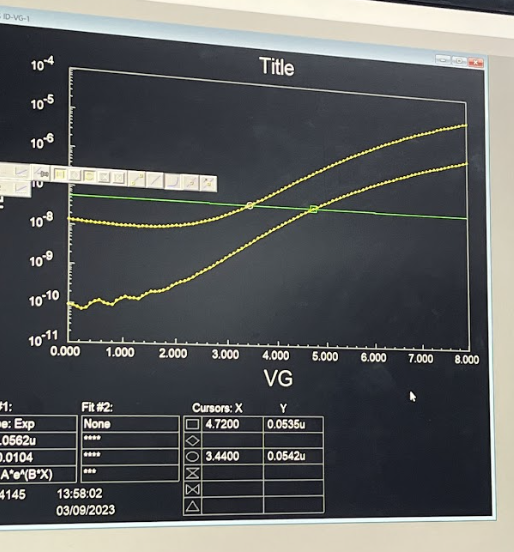

③ 6번째 die ) W=100, L=100um

- Vth = 4.12V

- I_on = 0.0751uA

- I_off = 0.0536nA

- SS = 1/1.2610= 0.7930

- DIBL = 0.6V

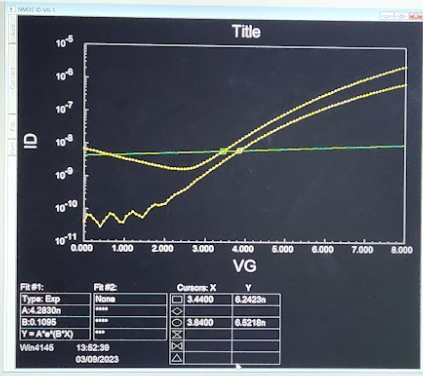

④ 6번째 die ) W=100, L=30um

⑤ 6번째 die ) W=100, L=10um

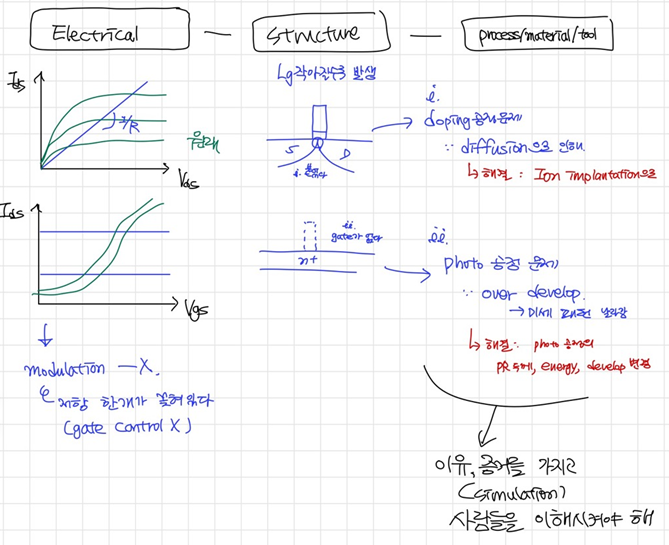

3. modulation. 왜 device가 측정되지 않았는지?

- 측정에서 왜 제대로 device가 작동하지 않았는지 구조적 관점 -> 공정적 관점에서 생각해 보아야 함.

- 위 과정을 제대로 설명하는 것이 문제 해결 능력!

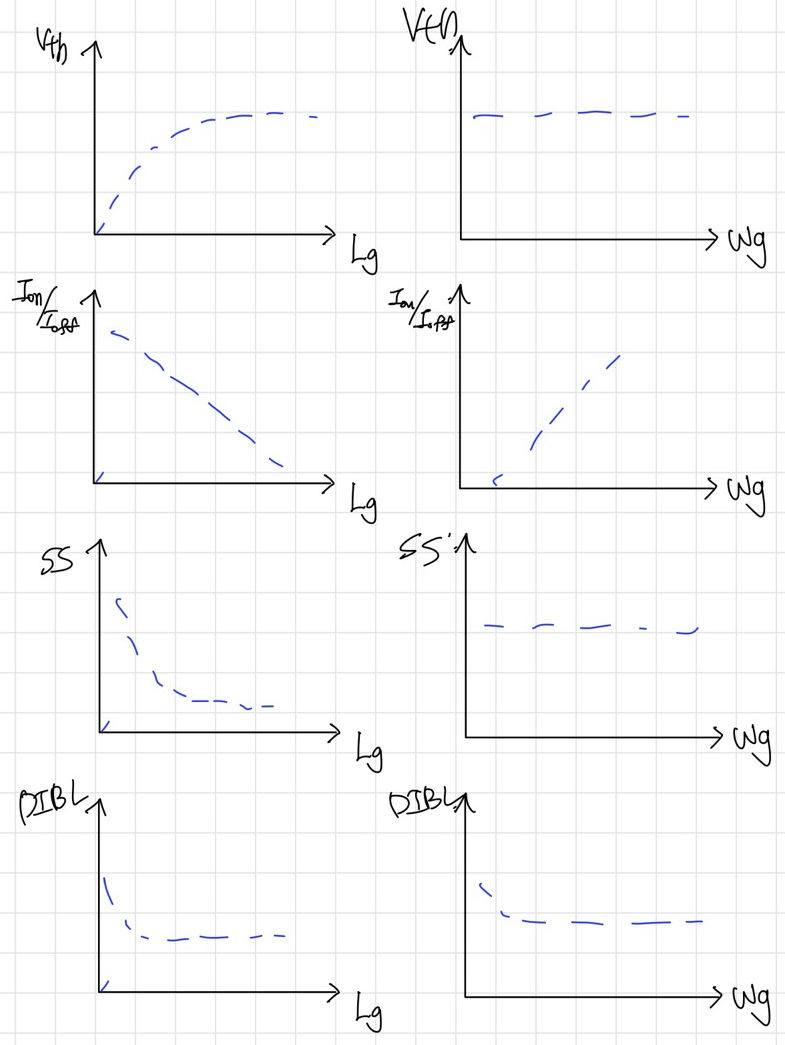

4. 측정 parameter의 경향

- 반도체 3가지 만족 요건 : Power↓, Performance↑, Area↓

5. 이상한 동작을 하는 device

ⅰ saturation되었다가 증가하는 전류값

- 구조가 어떻길래 갑자기 증가할까? 생각해보기

- Vds가 과도하게 증가하면, Source와 Drain의 depletion 영역이 증가, Punch Through가 발생하며 전류 증가

ⅱ 낮은 Vgs에서 큰 noise 발생

- 측정하는 장치의 한계.

- e-12가 최소값으로 지정되어 있어, 아래의 값은 noise가 크게 발생

ⅲ 직선처럼 보이는 그래프

ⅳ 반대로 흐르는 전류

-> 예상)

ILD etch가 과하게 진행되어서 source와 drain이 연결되었거나, 과식각으로 인해 gate가 제대로 된 역할이 하지 않음

4일동안의 공정실습이 끝이 났습니다..

자세한 후기와 소감은 다음 글에서 적어볼게요!