안녕하세요 바니입니다!

드디어 물리전자2의 꽃과 같은 MOSFET에 대한 글을 쓰네요.

이번 게시글에서는 mosfet의 구조와 다양한 characteristic을 중점으로 다뤄보겠습니다!

- MOSFET (Metal-Oxide-Semiconductor Field-Effect Transistor)

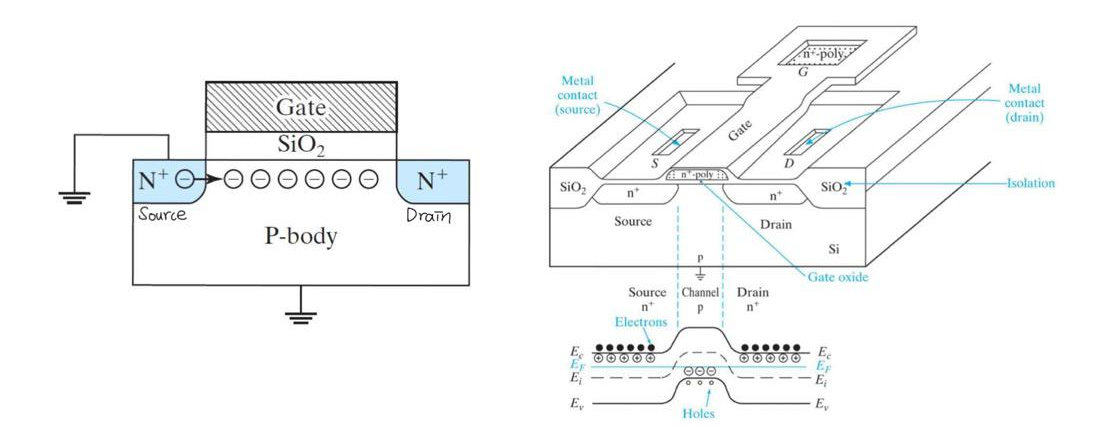

MOSFET의 기본구조는 위와 같습니다.

위에서 부터 Gate-SiO2-Semi 로 구성되어 있고, 반도체 쪽은 source, body, drain으로 구성되어 있습니다.

여기서 언급하는 MOSFET의 source와 drain은 같은 타입으로 도핑되어 있습니다.

그림에도 나와있지만, gate, source, body, drain에 인가하는 전압은 각각 V_G, V_S, V_B, V_D로 표현합니다.

이러한 MOSFET은 전류의 switching 역할을 수행하고,

source와 drain사이 body영역에 channel이 형성되면 전류가 흐르게 됩니다.

이러한 과정을 수도꼭지에 비유하여 설명하기도 합니다.

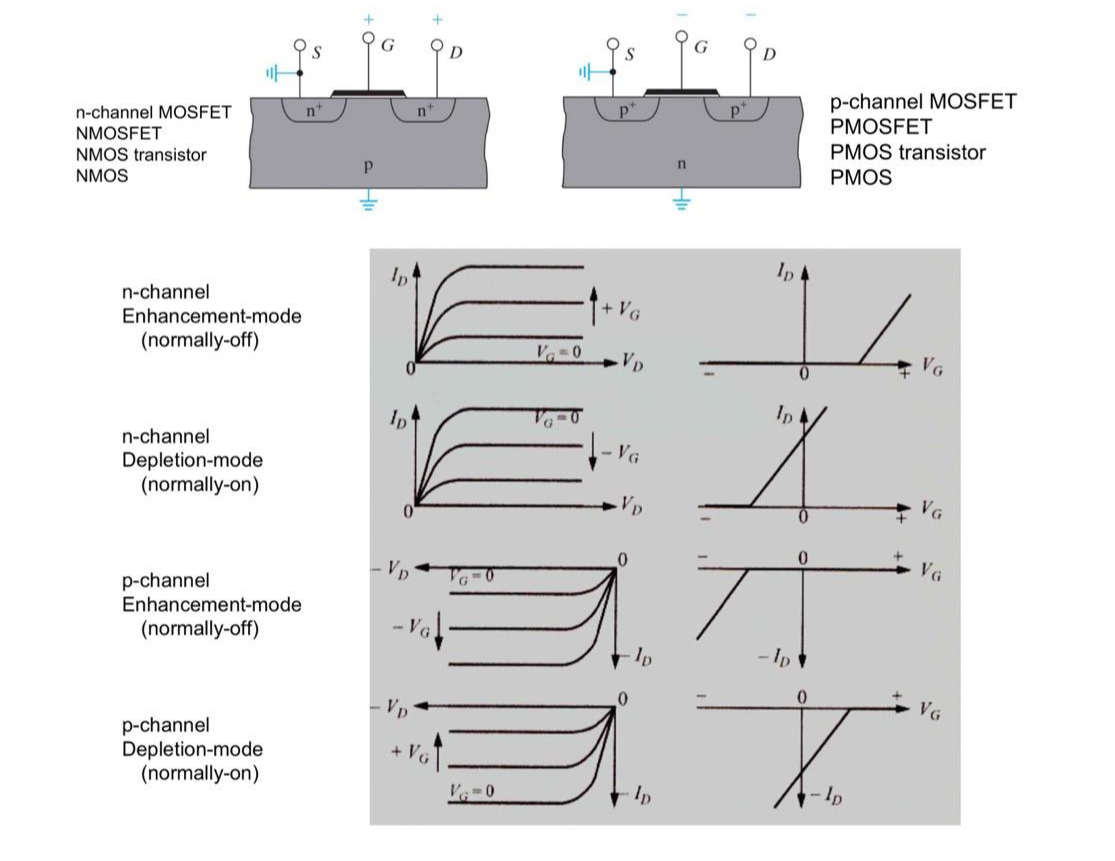

이러한 MOSFET은 크게 2가지의 종류가 있습니다.

channel이 어떤 종류로 inversion되는지에 따라 이름이 결정됩니다.

Enhancement-mode(nomally-off)는 gate전압이 0일 때는 꺼져있고, Depletion-mode는 gate전압이 0일 때 전류가 흐르게 됩니다.

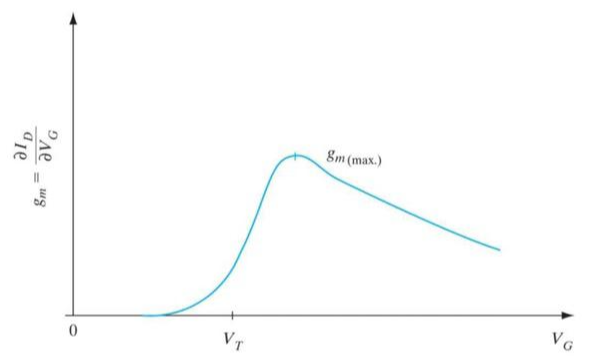

- Energy Barrier & I-V curves

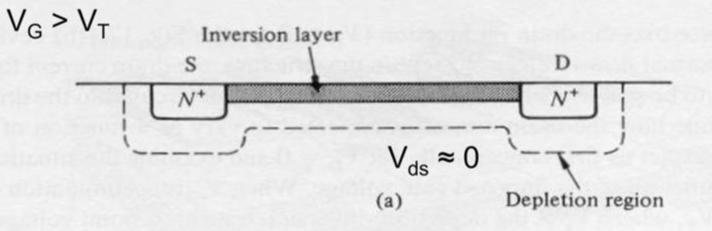

gate에 V_T(threshold voltage)보다 큰 값을 걸어주게 되면, channel이라는 inversion layer가 형성됩니다.

inversion layer가 형성되면 S와 D사이의 body의 energy band가 내려오게 되고 이로 인해 전하가 흐르며 전류가 흐르게 됩니다.

source와 drain의 energy barrier는 qV_D만큼의 차이를 가지고 있는데,

정확히는 V_DS = V_D - V_S이지만, source의 전류가 접지되어 있다고 가성하고 있어 V_D라 나타내고 있습니다.

그리고 MOSFET에서 주로 볼 수 있는 두 curve는 다음과 같습니다.

왼쪽 그래프는 Transfer characteristic(curve)로 gate voltage와 drain current로 이루어져 있습니다.

drain current는 오른쪽 축이 log scale, 왼쪽 축이 linear scale입니다.

오른쪽은 Output characteristic이고, drain voltage와 drain current로 구성되어 있습니다.

이 그래프에서 gate voltage가 증가할수록 그래프가 위로 증가하는 것을 알 수 있습니다.

- Qualitative theory of MOSFET

MOSFET에서 전류가 흐르기 위한 과정을 살펴봅시다.

(1) V_GS < V_T

이 상황에서는 inversion layer가 생성되지 않아 전류가 흐르지 못하게 됩니다.

(2) V_GS > V_T

① V_DS 가 거의 0에 인접

이 상황에서는 전류가 흐르지 않는 상황입니다. drain과 source의 전압이 같은 상황이죠.

하지만 PN junction에 의해 depletion region이 형성되어 있습니다.

② V_DS > 0

drain voltage가 source voltage보다 커졌기 때문에, 전류가 source -> drain으로 흐르게 됩니다.

즉, channel이 형성되고, reverse bias로 인해 depletion region이 증가하게 됩니다.

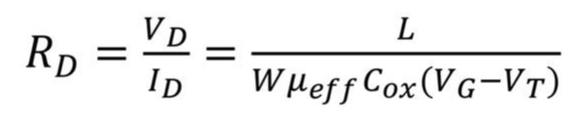

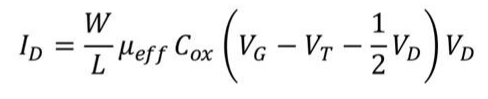

위 상황에서 흐르는 drain current를 수식으로 구해봅시다.

linear region에서 전류가 흐르기 위해서는 위에서 얘기한 것들을 정리하여,

일 때를 조건으로 말합니다. 그래서 I_D를 구하면,

그리고 channel의 저항은 옴의 법칙을 이용하여 다음과 같이 구할 수 있습니다.

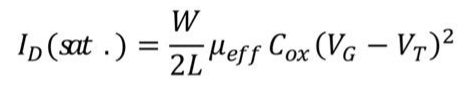

위 식에서 나오는 u('뮤')_eff는 얼마나 캐리어가 잘 흐르는지를 나타내는 요소로, effective carrier mobility라 합니다.

이 값은 다음과 같은 그래프의 형태를 나타냅니다.

이들의 관계는 물리전자1에서 언급되어 있는 'Scattering mechanism'으로 인해 설명가능합니다.

ⓐ Surface roughness scattering

MOSFET의 표면이 semi보다 더 평평해서, carrier가 표면의 영향으로 인해 더 느리게 이동한다

→ u_eff ↓

ⓑ Coulombic scattering

V_G가 (+)방향으로 커질수록, 흐르는 전자를 gate와 oxide방향으로 강하게 당기므로

→ u_eff ↓

ⓒ Phonon scattering

온도가 증가하면 → u_eff ↓

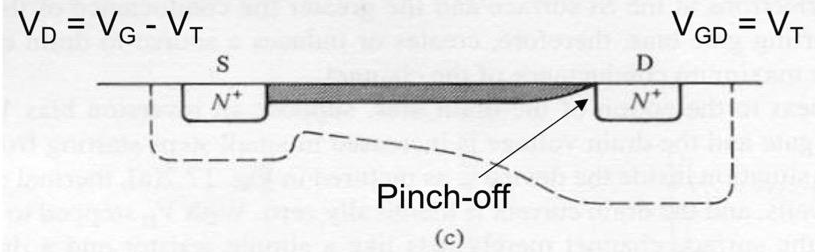

- Punch-off & Saturation region of operation

① V_D ≤ V_G - V_T

이 상황은 위에서 설명했던, inversion layer가 생성될 때입니다.

이때 추가된, V_D와 V_GT가 같을 때를 보면, drain쪽의 channel영역 끝부분이 둥글게 들어가며 닿아있는 것을 볼 수 있습니다.

이때의 상황을 Pinch-off 라고 합니다.

② V_D > V_G - V_T

이때는 △L에 inversion layer가 형성되지 못하고 channel이 끊기는 pinch-off 현상이 발생했습니다.

그리고 실제 channel에 걸리는 전압은 V_Dsat만큼 걸리게 됩니다.

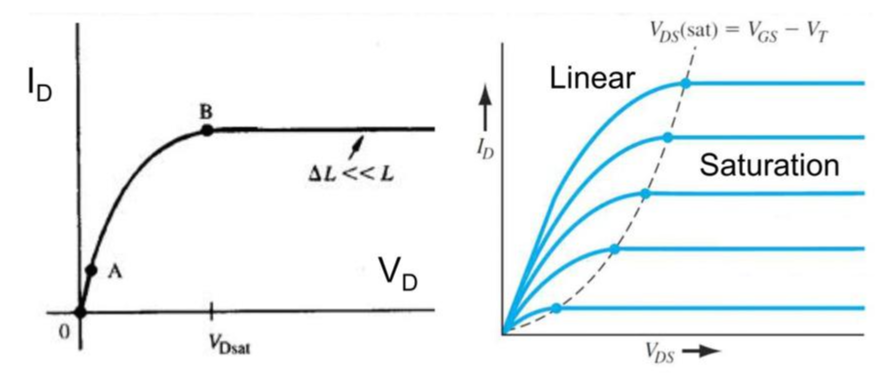

V_Dsat을 기준으로, 이전에는 drain current가 linear하게 증가하다가 이후로는 saturation하게 됨을 알 수 있습니다.

이 값은 V_Dsat = V_GS - V_T로 구할 수 있습니다.

이렇게 pinch-off가 발생하는 상황에서 △L이 L에 영향을 끼칠정도로 커지면, 전체 channel의 길이가 짧아지게 되는 것 처럼 보이게 되는데, 이러한 현상을 channel length modulation이라고 합니다.

위의 그래프와는 다르게, V_Dsat이후에서도 I_D가 증가하는 경향을 보이는데, 이 때가 바로 channel length modulation상황입니다.

이때는 다음 세가지 조건을 만족합니다.

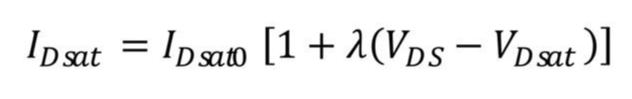

결론적으로, I_Dsat을 구하면,

위 식을 통해 V_DS와 V_Dsat이 같다면 channel length modulation이 발생하지 않는다는 것을 알 수 있습니다.

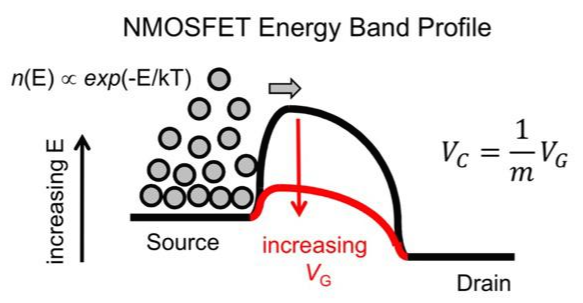

- Derivation of I-V

channel에서 current는 drift로 인해 흐르게 됩니다.

gate에 걸어준 전압으로 인해 SiO2에 E-feild가 생겨 전하들이 drift되기 때문이죠.

channel voltage를 Vx라 하면, Q_inv는 다음과 같이 나타낼 수 있습니다.

이를 이용해 drain current를 구해봅시다.

그리고 양 변을 적분하여 I_D를 구할 수 있습니다.

x=L만큼 충분히 inversion된 상태의 전류는 위와 같은 값을 가진다는 것을 알 수 있습니다.

- output curve

위에서 언급했지만, output characteristics는 I_D - V_D를 나타냅니다.

(1) linear region

이 영역에서는 전도도를 나타내는 conductance를 사용합니다.

(2) saturation region

이 영역에서는 transconductance를 사용합니다.

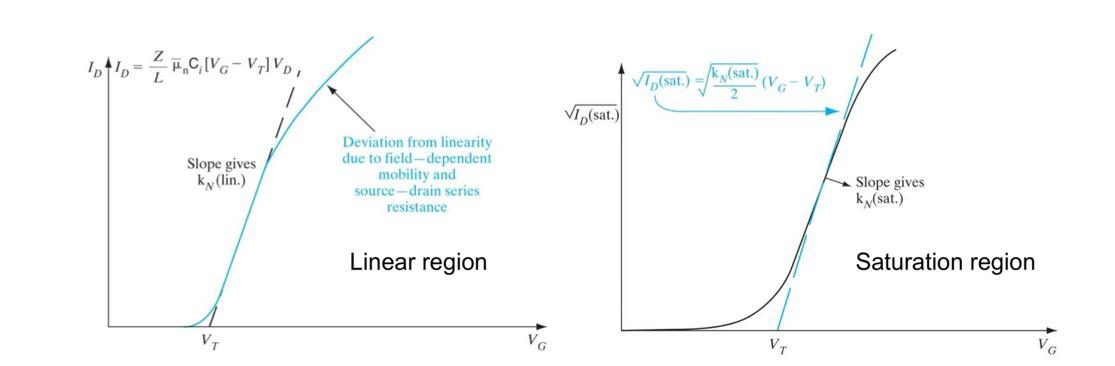

- transfer curve

transfer characteristics는 I_D - V_G를 나타냅니다.

① linear region

② saturation region

각 그래프의 기울기를 g_m으로 표현하고 다음과 같이 나타낼 수 있습니다.

- Subthreshold current

우리가 지금까지 본 상황들은 당연하게 이상적인 상황일 겁니다.

V_GS < V_T의 상황에서는 current가 흐르지 않는데, I_D가 흐르는 이상적이지 않은 상황을 생각해 봅시다.

linear scale보다 log scale을 보면 더욱 보기 쉬운데, V_T이전에서 I_D가 흐르는 것을 확인할 수 있습니다.

이렇게 V_T (threshold voltage)이전에 흐르는 current를 subthreshold current라고 합니다.

이 전류값은 on상태에서는 작은 값이지만, off상태에서는 큰 값을 보입니다.

그리고 V_G를 내리고 있는 중에 전하가 움직여 전류가 흘렀기 때문에,

subthreshold current는 전하의 diffusion으로 인해 발생한 전류가 됩니다.

그리고 이 subthreshold current를 나타내는 요인을 Subthrechold Swing (S / SS)라 합니다.

위 log scale의 그래프에서 기울기의 역수값을 가지고, current를 1칸 올리는데 필요한 V_G의 값을 의미합니다.

그리고 이 SS값은 다음과 같은 수식으로 표현할 수 있습니다.

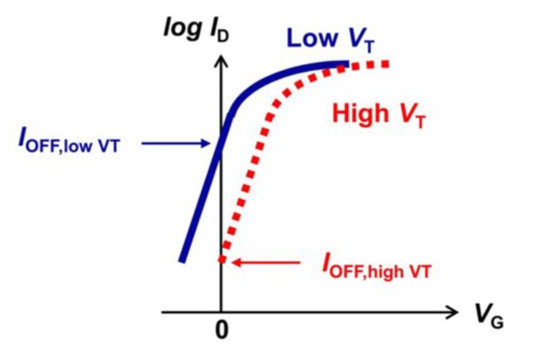

위 그래프에서 두 V_T를 비교할 수 있습니다.

우리가 원하는 이상적인 MOSFET은 on current는 크고, off current는 작아야 하지만,

실제로는 둘 다 증가하거나 둘 다 감소하는 움직임을 보입니다.

따라서, V_T를 design하려면 이 두 current의 trade off관계를 유의하여 디자인 해야합니다.

이번 글은 여기까지 입니다!

다음 글은 이에 이어서 MOSFET의 다양한 현상들에 대해 다루어 보려 합니다 (body effect, short channel effect ...)

얼른 물리전자2를 끝내고 다른 과목을 써보고 싶네요! 열심히 하겠습니다!!

읽어주셔서 감사합니다 :)

'[학부 일기] 전자공학과 전공 > 물리전자II' 카테고리의 다른 글

| [ 물리전자II ] BJT의 구조와 원리 (0) | 2022.03.17 |

|---|---|

| [ 물리전자II ] MOSFET의 구조와 원리 (2) (0) | 2022.03.14 |

| [ 물리전자II ] MOSCAP의 구조와 원리(2) (0) | 2022.03.04 |

| [ 물리전자II ] MOSCAP의 구조와 원리(1) (1) | 2022.02.21 |

| [ 물리전자II ] Metal-Semiconductor Junction (0) | 2022.02.15 |